文章编号:1671-4598(2023)11-0119-05 DOI:10.16526/j.cnki.11-4762/tp.2023.11.018 中图分类号:TP391

文献标识码:A

# 边界扫描在数模混合电路板级测试中的 设计与应用

# 王 晴1, 王祗女2, 张栋存1

(1. 航天科工空间工程发展有限公司,北京 100854; 2. 北京控制与电子技术研究所,北京 100038)

摘要:针对飞控系统某数模混合电路板测试需求,在不利用外部信号源、信号采集设备的条件下,利用边界扫描技术进行测试系统设计;介绍了PCI-410 边界扫描核心套件和 ScanWorks 测试软件,对边界扫描测试方法进行研究,详细说明了测试系统方案设计、测试流程开发步骤以及测试程序执行方式,并通过实际测试,验证了设计的可行性,为数字电路板和简单的数模混合电路板的测试提供了实用的测试方法和手段,具有很好的应用价值。

关键词:边界扫描;数字电路;数模混合电路;PCI-410;ScanWorks

# Design and Application of Boundary-scan in Board-level Test of Digital-analog Hybrid Circuit

WANG Qing<sup>1</sup>, WANG Zhiwen<sup>2</sup>, ZHANG Licun<sup>1</sup>

(1. CASIC Space Engineering Development Co., Ltd., Beijing 100854, China;

2. Beijing Institute of Control and Electronics Technology, Beijing 100038, China)

**Abstract:** For the testing requirements of a digital-analog hybrid circuit board of the flight control system, used boundary-scan technology to design the test system without using external signal source and signal acquisition equipment. Introduced the PCI-410 boundary scan core suite and ScanWorks test software, studied the boundary scan test method, described the test system scheme design, test flow development steps and test program execution method in detail, and verified the feasibility of the design through practical testing, which provided practical test methods and means for the test of digital circuit boards and simple digital-analog hybrid circuit boards, and had good application value.

Keywords: boundary-scan; digital circuit; digital-analog hybrid circuit; PCI-410; ScanWorks

## 0 引言

伴随着集成电路技术的数字化程度越来越高<sup>[1]</sup>,越来越多的电路板由 FPGA、CPLD、DSP 等大规模集成电路组成,这些体积小、集成度高的芯片为电路设计带来了巨大便利<sup>[2]</sup>。与此同时,超大规模集成电路、表面贴装等新技术也为电路的板级测试带来诸多难题<sup>[3]</sup>,传统的测试方法包括探针测试方法、内建自测试技术(BIST,Built-InSelfTest)、边界扫描测试技术。探针测试方法需要将物理测试探针置于被测电路的测试点上,从而开展电气性能测试<sup>[4]</sup>,工作准备流程繁琐,且开发人员需要预留一定数量的测试点,随着电路密度的不断增加,绝大部分电路板采用多层设计,几乎不可能设置足够多的探针测试点来完成整个电路的测试覆盖<sup>[5]</sup>,而且探针属于接触时测量,测试过程中还有对电路板本身造成损坏的潜在风险。内建自测试过程中还有对电路板本身造成损坏的潜在风险。内建自测试方是

间,降低了成本,但是这种测试方法往往对电路本身的引脚故障测试覆盖不足。边界扫描测试技术作为一种大规模数字集成电路测试标准,提供了一整套标准、完整的电路测设方法,利用移位寄存器和测试向量来控制集成电路管脚的状态,通过边界扫描链路实现对大规模集成电路全部管脚的控制,解决了高密度、高集成度数字电路板测试、故障造不足的难题,实现了电路的功能测试、静态测试、故障定位等<sup>[5]</sup>。本文从某数模混合电路测试入手,介绍了利用边界扫描测试技术进行数模混合电路测试的设计方法,在不采用外部信号源、采集设备的情况下,最大限度实现电路板的测试覆盖,有效降低的测试过程中的经济成本和时间成本,同时,也提高了测试效率。

# 1 边界扫描测试技术

边界扫描 (BS, boundary scan) 测试技术, 简称边扫, 正式命名来源于 IEEE/SNSI Standard 1149.1 - 1990 (后简称 IEEE 1149.1)<sup>[7-8]</sup>, 规定了利用边界扫描进行测试所需要

收稿日期:2023-05-16; 修回日期:2023-10-12。

作者简介:王 晴(1984-),女,硕士,高级工程师。

引用格式:王 晴,王祗文,张栎存. 边界扫描在数模混合电路板级测试中的设计与应用[J]. 计算机测量与控制,2023,31(11):119-123,130.

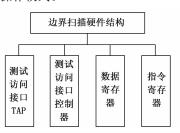

的硬件和软件,为相关的测试设计提供了完整的指导规范<sup>[5]</sup>。IEEE 1149.1 标准对于被测单元来讲属于非侵入式的测试方法,它不关心被测单元的内部程序,测试过程中在不对被测单元的内部程序做任何修改的情况下,仅依靠 JTAG 接口实现对逻辑电路各个引脚的控制。当前主流的 FPGA、CPLD、DSP等集成电路均支持该规范,利用该规范,也能够达到测试非边界扫描期间的目的<sup>[10]</sup>。边界扫描硬件结构组成主要包括 4 部分:测试访问接口(TAP)、测试访问接口控制器、数据寄存器(DR)以及指令寄存器(IR)<sup>[11-14]</sup>。

- 1)测试访问接口包括测试数据输入(TDI)、测试数据输出(TDO)、测试时钟(TCK)、测试模式选择(TMS)、信号复位(TEST),边界扫描测试运行主要依靠该接口进行数据控制和操作。

- 2) TAP 控制器作为一个含有 16 个工作状态的有限状态机,用于实现对测试访问接口的控制。

- 3)数据寄存器由 TAP 控制器决定存放测试过程中的测试数据和结果,包括旁路寄存器和边界寄存器。边界寄存器首尾连接构成链路,实现对芯片引脚的输出控制;旁路寄存器为不需要测试的位置提供一条快捷通道,缩短不必要的测试时间。

- 4) 指令寄存器包括串行/并行锁存寄存器,用来定义数据寄存器的操作模式。

图 1 边界扫描硬件结构组成

#### 2 边界扫描测试系统设计

#### 2.1 边界扫描硬件套件

PCI-410 边扫测试套件作为美国 ASSET 公司设计的一款 JTAG 控制器,具备高吞吐率、灵活配置和使用的特点,能够用于规模化量产测试以及需要多个 JTAG 端口同时测试的被测电路,可执行边界扫描测试软件开发的测试任务或烧录任务,支持扫描链路测试、互联测试、Flash 测试、存储器测试、用户自定义测试以及电路开短路测试等,依靠高速的 TCK 时钟和并行测试烧录能力,可作为大规模数字电路测试诊断的优选解决方案。

PCI-410 实物套件主要由 PCI 控制卡、4 端口边界扫描适配器以及相应的配套测试线缆组成。TCK 测试时钟最高运行速率可达 50 MHz,适配器与 PCI 控制卡之间的有效距离最高可达 15 米,便于测试系统集成。一个边界扫描控制平台可以支持在一个工作站上同时安装 3 块 PCI 控制卡、单块控制卡又可以同时支持 2 块适配器,每块适配器支持 4个 TAP 边扫接口,所以单个测试平台可以支持的边扫接口

高达 24 个。根据需要可以对被测电路灵活配置,并将多块不同的测试电路上的多个扫描链路串接成 1 条链路集中管理和测试,避免了过多的、非必要的链路管理。大规模量产测试时,也可以接多块相同的被测电路,对其执行相同的测试,并且 JTAG 接口的数据首发是并行的,可有效降低测试线路搭建、数据烧录的测试时间。同时,为了支持非边扫信号的测试需要,每个适配器还支持可独立控制的20 个离散 I/O 信号,每一路离散 IO 的电压可通过软件控制,且都配有终端可供灵活配置。

# 2.2 边界扫描软件平台

ScanWorks 嵌入式软件平台是 ASSET 公司基于 IEEE1149.1 标准设计的边扫测试集成开发环境,同时还支持 IEEE1149.6 标准,具有较广的应用范围。可提供整套完整的电路板边扫测试方案,对被测电路开展在线编程、测试和调试,并生成测试测试覆盖率报告[15-16]。 ScanWorks软件平台可根据被测电路网表文件以及边扫测试器件的 BS-DL 模型文件,通过合理配置生成测试需要的测试矢量,在线烧录数据,对测试程序进行单步、连续运行调试和测试执行。

通过 ScanWorks 软件平台进行测试程序开发前,有一些必要的准备工作需要提前了解:首先,确认被测电路板上的可编程器件是否含有 JTAG 接口,是否符合 IEEE1149.1 标准,都符合的情况下才可以进行边界扫描测试开发;其次,提前准备边界扫描测试元件的 BSDL 模型文件,可以向芯片厂商官网下载或者向 ASSET 技术支持请求;再者,提前准备非边扫器件的模型文件,便于互联测试开发;还有,被测电路板中如果含有 CPLD,最好提前将内部程序读取保存,型号较老的元件有可能在边扫测试时被擦除,导致电路板功能失效。

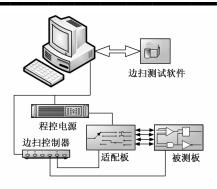

## 2.3 测试系统设计

边界扫描测试重点用于测试数字电路<sup>[17-19]</sup>,主要包括链路测试、互连测试、Flash测试、存储器测试以及用户自定义测试,用户自定义测试可以通过特殊设计,达到测试非边界扫描器件以及放大器、AD/DA 数模混合电路的目的。本文针对飞控系统某数模混合控制电路板的组成特点和测试需求,在尽量不适用外部外侧设备的条件下,满足被测电路板所有重要测试节点的故障诊断需要,构建如图 2 所示的边界扫描测试系统,主要包括测试计算机、边界扫描控制器、边界扫描测试软件、程控电源、测试适配板、被测电路板以及若干条配套测试线缆。其中,边界扫描测试硬件选用 PCI-410 套件;边界扫描测试软件选用 Scan-Works。

计算机作为整个测试系统的控制中心,利用 Scan-Works 软件完成边界扫描测试工程的开发、功能测试项的执行,用户自定义测试的激励发送和响应接收。PCI-410 套件作为作为连接边扫测试软件和被测电路板的桥梁,用于将边扫测试软件生成的测试矢量下发到被测电路板以及测试数据的采集。程控电源用于系统供电以及测试的自动化

图 2 边界扫描测试系统组成

运行。

对于含有模拟电路、很多没有互联模型的非边扫器件的数模混合电路板测试,为了提高测试覆盖率,关键技术是设计一套用于信号调理、边扫器件互联以及信号闭环的测试适配板,并通过用户自定义脚本的方式实现没有模型的无法进行互联测试的元器件的功能测试。测试适配板主要用于完成如下四部分功能: 1) 作为程控电源信号的转接接口,便于通过被测电路板供电连接器为被测电路板供电; 2) 信号调理,实现被测信号路由的电平匹配; 3) 为被测电路板对外输入、输出数字接口提供信号闭环; 4) 设计边扫器件及外围 DA、AD 电路,为被测电路板模拟信号接口提供信号闭环,最大程度覆盖电路板可测节点。有了信号闭环回路,便于通过互联测试和用户自定义测试的方式,提高整个电路板的测试覆盖。

#### 3 混合电路板级测试验证

#### 3.1 验证电路板需求分析

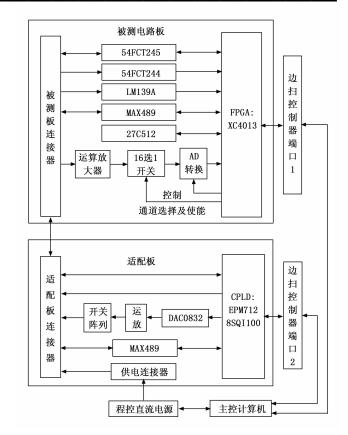

被测验证电路板采用飞控系统某数模混合电路组成,所含芯片种类主要包括型号为 XC4013E 的 FPGA、AD 转换器 AD1674、模拟开关 MAX306、运算放大器 AD5962、电压比较器 LM139A、差分芯片 MAX489、总线缓冲芯片54FCT244 和 54FCT245、存储类 PROM 芯片 27C512 等。且电路板含有高密度连接器,许多信号通过该连接器输入或输出,单板测试含大量信号未闭环。该验证电路板的边界扫描测试需覆盖所有主要芯片的信号路由通断故障、影响板子正常使用的所有重要数字引脚的开短路等故障,并精确定位到具体信号传输路经或者具体芯片引脚。

# 3.2 测试方案详细设计

根据被测电路板的测试需求,设计边界扫描测试系统, 其测试方案示意图如图 3 所示,通过合理设计适配板,完 成数字电路测试、模拟电路测试以及连接器开环信号的 测试。

被测电路板的存储器及其他信号闭环通路,可以直接 开发测试程序,通过边扫端口 1 控制 XC4013E 实现测试覆 盖。对于开环信号测试,根据被测电路板的信号类型和数 量,适配板选择可编程逻辑器件 EPM7128SQI100 作为边界 扫描主控元件,搭配外围电路实现被测电路的测试需求 覆盖:

图 3 验证板测试方案示意图

- 1) 边扫主控软件 ScanWorks 导入被测板和适配板的网表文件和模型文件,通过配套硬件开发套件 PCI-410 控制被测板和适配板上的边扫器件 FPGA 和 CPLD,再通过可编程器件的接口控制,实现软硬件接口的匹配;

- 2) EPM7128SQI100 的部分 IO 引脚以信号调理或者直接的方式,通过适配板连接器连接至被测板连接器,实现被测电路板开环数字信号的测试;

- 3) 针对被测电路多路运算放大器和 AD 的测试需要,适配板设置 DA 芯片、电流/电压运算放大器、开关阵列等,通过边扫端口 2 控制 EPM7128SQI100,实现 DA 信号的输出,进而通过开关阵列和连接器连接至被测电路 AD 采集通道,通过边扫端口 1 控制 XC4013E 实现模拟信号的测试;

- 4) 针对被测电路差分信号的测试需要,适配板设置相同的差分电路,单端信号接边界扫描芯片,差分信号通过连接器连接至被测电路的差分通道;

- 5) 放置供电连接器,直连程控直流电源的输出通道, 进而通过适配板连接器实现被测电路的供电。

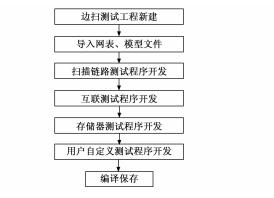

#### 3.3 边界扫描测试流程开发

为了完成被测电路板扫描链路完整性测试、互联测试、 存储器测试、用户自定义测试等测试需要,边界扫描测试 流程开发流程图如图 4 所示,依次为边扫测试工程新建、 网表文件和模型文件的导人、扫描链路测试程序开发、互 联测试程序开发、存储器测试程序开发;用户自定义测试 程序开发、测试程序的编译和保存等。测试流程开发前, 需要提前做一些准备工作: 备好被测电路板和适配板的原理图、网表文件、边扫器件的 BSDL 模型、非边扫数字器件的测试模型等。

图 4 边界扫描测试流程开发流程

# 3.3.1 边扫测试工程新建

工程新建用于为整个工程建立统一管理,同时导入和 编译边扫器件的 BSDL 模型,为后续测试工作做准备,工 程新建步骤如下:

- 1) 启动 ScanWorks 边界扫描开发程序;

- 2) 在弹出的软件启动向导界面单击 "close" → "Go to the interface" 进入边扫测试主界面,ScanWorks 自动识别已连接到主机的边扫开发套件 PCI-410;

- 3) 单击菜单栏 "project" → "new",在新建工程对话框填入工程名称以及存放路径,进行工程创建;

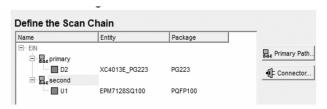

- 4)填入工程设计名称,并手动创建扫描链路:分别添加添加边扫器件的 BSDL 模型 7128sq100.bsd 和 xc4013e\_pg223.bsd,并编译检查模型文件是否正确;

- 5) 建立 HGL1. hgl 文件,包含上述的两个 BSDL 文件, 用于描述了测试板的边界扫描器件以及扫描链路信息,并 再次编译,根据报告提示进行查看或修改,完成边扫测试 工程的建立,HGL1. hgl 建立完成的界面如图 5 所示。

图 5 新建成功的.hgl 文件

#### 3.3.2 网表和模型文件导入

ScanWorks 软件支持多个电路板的网表文件自动合并,便于多个电路板的扫描链路集中统一管理,提高了测试效率。网表和模型文件导入步骤如下:

- 1) 软件菜单栏单击 "design" → "netlist";

- 2)分别导入被测板和适配板网表文件(也可以提前将被测板原理图和适配板原理图合并,导入一个统一的网表);

- 3) 网表文件添加成功后进行编译,根据报告提示进行查看或修改,完成网表文件的导入;

- 4) 指定网表文件中那些的电源和地线网络,测试时忽略该网络的测试;

- 5) 导入可以互联测试的非边扫器件模型文件,进行器件位号和模型的关联,并设置每个元器件的测试类型,如协议簇测试、忽略测试等,设置完毕后完成模型文件的导入。

#### 3.3.3 扫描链路完整性测试程序开发

扫描链路完整性测试可以检测边扫框架的物理故障, 比如测试总线、TAP控制器等。同时还可以验证工程建立 之初所描述的扫描链路顺序是否正确。Scanworks 自动产生 链路测试集,通过之前的描述,来报告故障位置。扫描链 路完整性测试开发步骤如下:

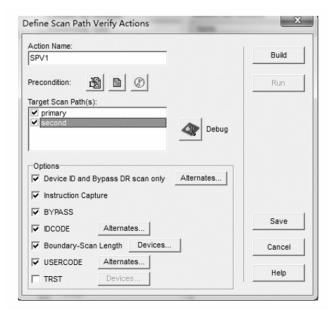

- 1) 在 Scanworks 主界面下双击 create an action 栏下的 scan path verify, 弹出 define scan path verify actions 对话框;

- 2) 在弹出的 define scan path verify actions 对话框中自动罗列测试工程新建过程中导入的两个边扫器件扫描链路,如图 6 所示:

- 3)在 Target Scan Path (s)中通过勾选左侧复选框进行边扫链路选择,如果两个同时勾选,软件则会将被测板边扫链路和适配板边扫链路打包成同一个链路进行集中测试:

- 4) 在 Options 中可以对要进行的边界扫描测试项进行选择, 比如 BYPASS、IDCODE、USERCODE、边扫链路长度等;

- 5) 单击右上角的编译按钮,查看编译报告,如果编译失败则根据报告窗口信息提示进行修改,直到编译通过为止(有警告也算编译通过),编译通过后完成扫描链路完整性测试的开发。

图 6 扫描链路选择

# 3.3.4 互联测试程序开发

互联测试允许测试边扫器件互联或者边扫器件与非边扫器件的互联,互联测试可以检测开路、短路、固高固低

或者桥接故障。

实际的被测电路中,基本都存在大量的非边扫器件,他们都会与边扫器件构成关联。测试过程中,如果测试程序不能识别非边扫器件,可以将其相关的网络暂时挂起,互联测试时忽略该网络;如果提前准备好了非边扫器件的模型文件,或者这些非边扫器件只是一些简单的缓冲器件、路由选择器件,可以通过互联测试中的簇测试进行测试。互联测试开发步骤如下:

- 1) 在 Scanworks 主界面下双击 create an action 栏下的 interconnect, 弹出 define an interconnect action 对话框;

- 3) 此时 define an interconnect action 界面的 model device 和 define constrains 可能处于非激活状态。进行编译并查看编译报告,如果编译失败则根据报告窗口信息提示进行修改,直到编译通过为止(有警告也算编译通过);

- 4) 单击 model device 打开 device browser 对话框,对非边扫器件进行 device type 设置: 电容设置为 capacitor、电阻设置为 resistor等;

- 5) 关闭 define an interconnect action 对话框,在边扫主界面可以看到一个名为 interconnect1 的互联测试项,将边扫控制的 TAP1 和 TAP2 端口分别连接至被测电路板和适配板即可执行互联测试。

#### 3.3.5 存储测试程序开发

由于被测存储器件没有找到测试模型,所以根据芯片 手册的时序逻辑,通过用户自定义的方式进行测试开发, 测试步骤如下:

- 1) 在 Scanworks 主界面单击 design→buses 来进行测试 总线定义,用于测试存储器的地址写和数据读;

- 2) 点击 new 框, 创建一个 8 位数据总线, 并打开 define a bus 对话框进行数据总线与存储器数据引脚的匹配设置, 在 bus manager 界面为已经定义的数据总线设置使能控制端;

- 3) 点击 new 框, 创建一个 12 位地址总线, 并打开 define a bus 对话框进行地址总线与存储器地址引脚的匹配设置, 在 bus manager 界面为已经定义的地址总线设置使能控制端;

- 4) 双击边扫软件主界面 create an action 下的 macro, 进行测试代码的编辑,编辑完保存关闭;

- 5) 在返回的 define a macro action 界面的 target 栏下选择 entire path,并进行编译,查看编译报告,如果编译失败则根据报告窗口信息提示进行修改,直到编译通过为止(有警告也算编译通过);

- 6)编译通过后保存,完成存储测试程序的开发。

# 3.3.6 用户自定义测试

根据 3.3.4 节存储器测试程序开发步骤,编写 macro 专 用测试代码,实现被测电路板的运算放大器和 AD 等器件的 测试。

# 3.4 边界扫描测试程序执行

测试程序开发完毕后,连接验证板和边界扫描控制器,

利用 Scanwork 软件进行测试程序执行的步骤如下:

- 1) 在 Scanworks 主界面单击菜单栏 TOOL→select hardware,选择测试台边扫仿真器件 PCI-410;

- 2) 通过程控直流电源给被测板和适配板供电;

- 3) 给被测板加电后选择边扫工程文件下的 action, 单击 buile-run, 执行测试并查看结果。

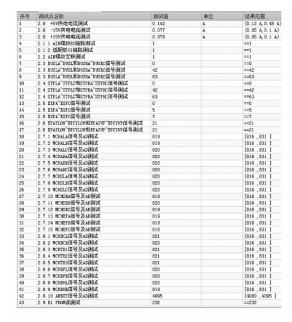

# 4 测试结果与分析

为了便于测试程序的自动化运行,通过主控计算机专用测试软件,对 Scanwork 软件进行二次集成开发,自动调用程控直流电源进行供电,自动调用边界扫描测试程序执行并上传测试结果。被测电路板最终测试报表如图 7 所示:第 1~3 项为电路板供电测试,首先判断电路板正常工作的功率是否满足要求;第 4~5 项为被测电路板和适配板上的边扫器件的扫描链路测试,检查边扫器件是否有故障;第 6 项为互联测试,检查边扫器件互联和边扫器件与有模型的非边扫器件的互联,判断互联测试的元器件有无开短路、固高固低或者桥接等故障;第 7~42 项为用户自定义测试,通过编写测试脚本检查没有模型的非边扫器件的功能是否正常;第 43 项为存储器测试。每一项测试记录均设定测试结果的合格判据,自动给出测试结果,可为电路板功能测十 试和故障诊断提供有力支撑。

图 7 被测电路板测试报表

为了进一步验证测试程序的有效性,通过人为焊接方式制造了3处 XC4013E的 IO 引脚短路故障、1 处存储器地址引脚短路故障和1 处总线缓冲芯片的开路故障。通过测试程序执行,均成功检测出故障并定位故障位置,进一步验证了边界扫描测试系统设计的正确性。

# 5 结束语

本文提出的边界扫描测试系统设计方法,适用于不利用 (下转第130页)