Computer Measurement & Control

文章编号:1671-4598(2023)01-0276-06

DOI:10.16526/j. cnki. 11-4762/tp. 2023. 01. 041

中图分类号:TN432

文献标识码:A

# 10~26 GHz CMOS 六位数控衰减器设计与实现

# 维寒阳<sup>1,2</sup>、季 斌<sup>1</sup>、陈卫东<sup>1</sup>

- (1. 中国电子科技集团公司 第五十四研究所, 石家庄 050081;

- 2. 河北省电磁频谱认知与管控重点实验室, 石家庄 050011)

摘要:为了使衰减器更好的适应相控阵系统对高集成度波束赋形电路的应用需求;基于 55 nm CMOS 工艺,设计了一款具有低插入损耗、低附加相移特性的六位数控衰减器,该数控衰减器采用桥 T 和  $\pi$  型衰减结构级联而成,在  $10\sim26$  GHz 频率范围内实现步进为 0.5 dB、动态范围为  $0\sim31.5$  dB 的信号幅度衰减;为减小插入损耗,NMOS 开关采用悬浮栅和悬浮衬底连接方式,同时采用了电容补偿网络和电感补偿以有效降低附加相移;仿真结果表明,在  $10\sim26$  GHz 的频带范围内,该数控衰减器的插入损耗小于-7 dB,输入/输出回波小于-10 dB,附加相移小于 $\pm3^\circ$ ,所有衰减态的衰减误差均方根小于 0.8 dB,芯片的核心电路面积为 0.36 mm $\times0.16$  mm。

关键词:集成电路技术;数控衰减器;CMOS;NOMS开关;附加相移

# Design and Realization of a 10~26 GHz CMOS 6-Bits Digital Attenuator

LUO Hanyang<sup>1,2</sup>, LI Bin<sup>1</sup>, CHEN Weidong<sup>1</sup>

- (1. China Electronics Technology Group Corporation No. 54 Research Institute, Shijiazhuang 050081, China;

- 2. Hebei Key Laboratory of Electromagnetic Spectrum Cognition and Control, Shijiazhuang 050011, China)

Abstract: In order to make attenuators better meet the application requirements of high integration beamforming circuit in phased array system, based on 55 nm CMOS technology, a 6-bits digital attenuator with small phase variation and low insertion loss is designed. The digital attenuator is cascaded by using the bridge T and  $\pi$  structures, and a dynamic attenuation range from 0 to 31.5 dB with a step resolution of 0.5 dB is realized in the frequency range of  $10\sim26$  GHz. In order to reduce insertion loss, floating gate and floating body are adopted in NMOS switch. In addition, inductance compensation and capacitance compensation network are used to achieve low phase variation. The simulation results show that in the frequency range of  $10\sim26$  GHz, the insertion loss of the digital attenuator is less than -7 dB, the input and output reflection wave less than -10 dB, the additional phase shift less than  $\pm 3^{\circ}$  phase for all attenuation state, the RMS error of attenuations less than 0.8 dB, the total chip size excluding pads is 0.36 mm $\times$ 0.16 mm.

Keywords: integrated circuit technique; digital attenuator; CMOS; NMOS switch; additional phase shift

# 0 引言

相控阵系统因其波束指向精确度高、波束合成快以及其快速波束扫描能力被广泛应用于雷达[1]。相控阵的优异特性源于其每个天线单元都有一个 T/R (接收/发送)组件。而数控衰减器作为相控阵收发组件的核心组成单元,主要用于提供精确的信号幅度控制来抑制副瓣电平和补偿通道间增益误差[2]。为了满足相控阵系统的高性能、高精度、小型化需求,对数控衰减器的性能提出更高要求,即在保证衰减线性度的同时还必须降低衰减器插入损耗[3]和附加相移[4]。衰减器分为有源衰减器和无源衰减器两大类。有源衰减器主要是基于可变增益放大器,通过改变负载的值来改变衰减器的增益,最后利用数字电路将连续变化的增益进行离散化[5-7]。与有源衰减器相比,无源衰减器的功耗几乎为零,并且线性度高。无源衰减器主要有分布式结构、开关路径结构以及开关 T/II 结构,以上几种衰减结构

主要通过控制射频开关来实现不同的衰减状态[8-10]。与分布式衰减结构和开关路径型结构相比,开关  $T/\Pi$  结构具有低插入损耗与较小的芯片面积等优势[11]。

采用 GaAs 等化合物工艺制作的数控衰减器,虽然具有低插入损耗、高线性度等优点,但其高成本、低集成度等缺点限制了其在大规模相控阵中的应用。相对于半导体工艺,硅基 CMOS(complementary metal oxide semiconductor)工艺具有高集成度、低功耗和低成本等优势<sup>[12-13]</sup>,但由于硅衬底的低阻抗特性,MOSFET(metal-oxide-semiconductor fieldeffect transistor)器件在射频频段寄生电容对电路的性能影响较大,采用硅基 CMOS 工艺设计的衰减器在高频下实现高精度、低附加相移的难度较大<sup>[14-18]</sup>。近年来,随着硅基工艺的快速发展,GaAs 化合物工艺的高频性能逐渐可以被硅基工艺代替,硅基工艺器件的截止频率逐渐提高使得利用硅基工艺进行无源衰减器的设计成为现实<sup>[19-22]</sup>。

目前在系统产品方面,国外研究机构已经研制出了系

收稿日期:2022-11-14; 修回日期:2022-11-17。

作者简介: 維寒阳(1998-), 男, 河北石家庄人, 硕士研究生, 主要从事射频集成电路方向的研究。

引用格式:維寒阳,李 斌,陈卫东.10~26 GHz CMOS 六位数控衰减器设计与实现[J]. 计算机测量与控制,2023,31(1):276-281,300.

列化的基于 CMOS 工艺的高集成度相控阵芯片,大大缩小了整个系统的体积和功耗[28]。显著简化了监控、卫星通信所用的相控阵雷达系统尺寸、重量及功耗,尤其是在平面阵中的应用。国内 CMOS 毫米波相控阵芯片自主化也取得了一定成果。但未有得到大规模应用,与国外技术存在一定差距[24]。

本文以 CMOS 数控衰减器为研究对象,基于 55 nm CMOS 工艺设计了一款 10~26 GHz 的六位数控衰减器 (步进 0.5 dB,最大衰减量 31.5 dB,共有 64 个衰减状态),该数控衰减器采用 6 位数字信号对 6 个衰减位进行控制,该数控衰减器在整个带宽内在保证了衰减精度在 0.8 dB 下的同时具有良好的附加相位特性,衰减器附加相移在 3 以内。经过 MOS 管结构优化后的衰减器参考态插入损耗小于一7 dB。输入输出回波损耗均在一10 dB 以内,满足了相控阵系统在射频频段的工作需求。

# 1 衰减器分析与设计

本小节主要介绍衰减器的基本原理,定性分析各个结构的优势以及前仿真的初值计算问题。然后介绍 MOS 管的优化方法及效果。

#### 1.1 衰减结构分析

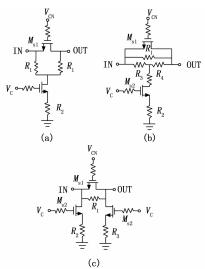

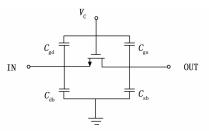

开关内嵌型衰减器主要的结构有 T 型、 $\pi$  型以及桥 T 型。本文主要采用 T 型和  $\pi$  型结构。T 型电路结构如图 1 (a) 所示,这种电路结构有源器件少,衰减精度较高同时产生的插入损耗低,但衰减振幅范围小,比较适合衰减幅度较小的衰减单元。对于本文采用的两种结构都是通过改变 MOS 管开关的状态来改变电路的工作状态,主要通过调节接地电阻阻值来改变衰减量。当  $M_{S1}$ 导通时,信号通过一条低损耗通路,此时的插入损耗来源主要于  $R_1$  和  $M_{S1}$ 的导通电阻。当  $M_{S1}$  截止, $M_{S2}$  导通时,信号被 T 型电阻网络衰减。

图1 经典衰减结构

在计算电路结构的电阻初始值时,为了保证电路在级联时的性能,我们要先将输入输出端口与特征阻抗 (50  $\Omega$ ) 进行匹配:

$$R_1^2 + 2R_1R_2 - Z_0^2 = 0 (1)$$

此时衰减量与电阻阻值的关系为:

$$LR_1 + (L-1)R_2 + Z_0L = 0 (2)$$

其中: L 是衰减量,  $Z_0$  是特征阻抗, 一般取 50  $\Omega$ 。

$\Pi$  型结构与 T 型结构类似,如图 1 (b) 所示,通过改变  $M_{S1}$ 和  $M_{S2}$ 的开关来改变电路的状态。 $\Pi$  型拓扑结构适合大衰减量单元。 $M_{S1}$ 导通时, $M_{S1}$  管等效为一个较小的导通电阻, $M_{S2}$  管此时关断等效为一个大的关断电容,此时信号没有经过衰减路径。当  $M_{S1}$ 关断, $M_{S2}$  管导通时, $M_{S1}$  管等效为一个大的关断电容, $M_{S2}$  管此时等效为一个小的导通电阻。部分信号流经  $\Pi$  型衰减网络进行衰减。

我们利用与特征阻抗匹配得到衰减量与电阻的关系:

$$R_1 R_2^2 - 2Z_0^2 R_2 - R_1 Z_0^2 = 0 (3)$$

$$LR_1R_2 + (L-1)Z_0R_2 + LZ_0R_1 = 0 (4)$$

桥 T 型结构如图 1 (c) 所示,由于  $R_1$  像"桥"一样横跨在  $Z_0$  上,两个  $Z_0$  和  $R_2$  构成上述的 T 型衰减网络。这种结构的特点是输入输出端口的驻波特性良好,输入阻抗等于输出阻抗。实际上,桥 T 型网络可以看做 T 型网络的进阶结构,它的衰减量由 T 型桥网络决定。因其良好的驻波特性决定了其可以很好的与其他衰减位级联。当输入输出端口匹配时衰减量和电阻之间的关系为:

$$R_3 = R_4 = Z_0 (5)$$

$$R_1 R_2 = Z_0^2 \tag{6}$$

$$L = \frac{R_2}{Z_0 + R_2} = \frac{R_1}{Z_0 + R_1} \tag{7}$$

但是由于其本身结构导致桥 T 型衰减网络的插损较大, 所以本文不再进行相关仿真实验。

# 1.2 附加相移分析

信号通过衰减器时,器件不仅会对信号的幅值产生影响,还会产生信号相位的偏移。在最终仿真时,我们可以用  $S_{21}$ 的相位差值来表示附加相移。

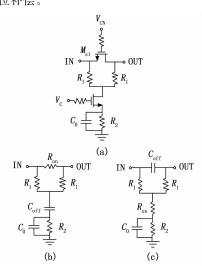

对于 T 型结构的衰减单元,由图 2 (b) 中可以看出,当电路处于参考状态时,MOS 管的关断电容  $C_{\rm off}$  使得电路可以看成一个低通滤波器。当电路处于衰减状态时,由于其直通路径上的关断电容  $C_{\rm off}$  使得电路可以看成一个高通滤波器。当信号通过两种状态的电路时,信号的相位将会发生变化。参考态电路信号的相位将会是滞后而衰减态电路的信号相位将会超前。并且由于该衰减器工作频率较高,容性电抗的变化对两个状态相位的影响随着频率的升高越来越大。

电路的附加相移就是衰减态和参考态的相位之差,在 进行电路设计时,我们一般很难做到两者之间差值为0,这 种引起的相位损耗我们一般要尽可能减小。一般我们采用 相位补偿技术来改善电路的相位特性。因为衰减态的等效 电路是一个使相位超前的高通滤波器,所以在并联通路中 引入一个并联电容或串联电感来补偿信号的相位,在综合 考虑插入损耗以及芯片面积后,我们采用并联电容来进行 衰减器的相位补偿。

图 2 T型衰减网络及其等效电路

在图 2 (b) 所示的等效参考态电路中,由于  $M_{\rm S1}$  的导通电阻  $R_{\rm on}$  远远小于  $R_{1.2}$ ,因此增加并联电容的参考态等效电路与传统的 T 型结构参考态等效电路信号相位基本一致。在衰减态等效电路中,补偿电容  $C_0$  短接到地构成了一个低通滤波器,由于低通滤波器有相位延迟特性,所以我们可以有效的降低衰减态与参考态的相位误差。通过调节低通滤波器器件参数,可以使并联电容结构的衰减态信号相位在工作频率十分接近传统结构。因此, $R_{1.2.3}$ 、 $C_0$  不仅作为电阻衰减网络衰减信号同时还构成了相位矫正网络。本文设计的相位矫正网络与文章 [15] 描述的相位/衰减矫正网络相比,低通滤波器可以作为原始电路中的一部分,没有增加额外的平行信号通路,也就大大减小了插入损耗。在衰减器电路等效模型的基础上,信号的相位为:

$$\theta = -\tan^{-1}\frac{C_0R_1^2R_3^2}{(R_1^2 + 2R_3R_1)(R_1 + R_3) + (\omega C_0R_3)^2R_1^2}$$

(8)

其中:考虑电路的对称性  $R_1 = R_2$ ,  $\omega$  为衰减器的工作 频率。

衰减态  $M_{52}$ 的导通电阻远远小于  $R_3$ ,所以忽略其影响。通过上式可知,本文设计的并联电容补偿网络可以有效降低由于关断电容  $C_{\text{off}}$ 所造成的相位超前的影响。在实际设计中,随着衰减器工作频率升高,并联电容还会对衰减器的线性度造成影响,所以需要综合考虑线性度和附加相移等因素进行设计。

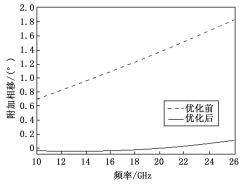

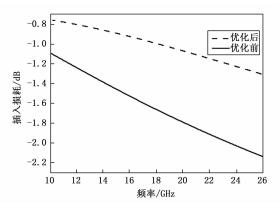

以 4 dB 衰减位为例,图给出了并联支路在采用了并联 电容补偿网络与不采用并联电容补偿网络情况下附加相移 的对比。由图 3 可知,不采用并联电容补偿网络的电路附 加相移在 1.8°以内,通过增加并联电容可以看到电路的附加相移在 0.2°以内。另外,随着频率的上升,参考态与衰减态的相对相位逐渐增大,主要是随着频率的升高,寄生电容对信号的影响逐渐增大。

图 3 优化前后附加相移对比

#### 1.3 0.5 dB 和 1 dB 电路

$0.5 \, \mathrm{dB}$  和  $1 \, \mathrm{dB}$  采用如图 4 (a) 所示的简化 T 型结构,以  $0.5 \, \mathrm{dB}$  为例,通过计算发现,T 型结构的两个对称电阻  $R_1$  阻值大约为  $1.34 \, \Omega$ ,基于 CMOS  $55 \, \mathrm{nm}$  工艺,在版图中用微带线代替,所以将原电路结构简化为如图  $2 \, \mathrm{m}$  示。此种结构电路的插入损耗低、附加相移小,并且版图面积小。在传统 T 型衰减网络中移除掉串联之路上的 MOS 管开关可以减小 MOS 导通电阻对衰减误差的影响,并且在降低 MOS 寄生电容对信号参考态和衰减态的相对相位影响。在设计中  $0.5 \, \mathrm{dB}$  和  $1 \, \mathrm{dB}$  采用简化的 T 型衰减结构,可以使得插入损耗降低  $4 \, \mathrm{dB}$  左右,但是简化后的衰减网络在电路级联时造成了阻抗失配。此问题的解决方案在文章  $1.7 \, \mathrm{节}$  进行电路级联时进行解决。当  $V_c$  处于高电平时电路处于衰减状态,反之处于参考态。

图 4 实际电路结构

#### 1.4 2 dB 和 4 dB 电路

2 dB 和 4 dB 衰减采用如图 4 (b) 所示改进的 T 型衰减结构, $V_{\text{C}}$  和  $V_{\text{CN}}$ 是一对相反的电平。当  $V_{\text{C}}$  处于高电平时,电路处于衰减状态;当  $V_{\text{CN}}$ 处于高电平时,电路处于参考状态。根据二端口网络中传输矩阵和散射矩阵的关系,分析可以得出电路的附加相移与 MOS 管的截止电容和导通电阻有关,并且在实际设计中,很难做到衰减相位与参考相位一致。为了降低 T 型网络结构在大衰减量设计时的附加相移,在经典结构的基础上增加了并联电容补偿网络。

此外,经过计算和仿真验证,2 dB 和 4 dB 的衰减结构中串联电阻阻值较小,需要在版图中依据前仿真结果自行设计电阻,其余电阻均可以采用工艺库中的电阻。

### 1.5 8 dB 和 16 dB 电路

随着衰减量的增大,T型衰减电路无法满足基本衰减单元需求。当T型衰减电路处于衰减状态时,MOS管的导通电阻和接地电阻将会对射频信号产生衰减,衰减量与二者的关系:

$$RL = 20\log\left(\frac{Z_0}{2R + Z_0}\right) \tag{9}$$

$$L = \left[1 - \left(\frac{Z_0}{2R + Z_0}\right)^2\right] \frac{R}{R + Z_0} \tag{10}$$

其中: R 是导通电阻和接地电阻的和, RL 是电路的回波损耗。

分析可知,随着 R 的减小,电路的回波损耗变差,当衰减量达到 8 dB 时,回波损耗急剧恶化,影响单级电路性能。由此可见, T 型结构的优势随着衰减量的增加而消失。所以 8 dB 和 16 dB 的衰减电路采用如图 4 (c) 所示的  $\pi$  型结构进行设计。由于衰减量较大以及 MOS 管数目的增多, 8 dB 和 16 dB 电路对参考态和衰减态的相对相位影响较大,因此在衰减接地电阻处采用增加并联电容补偿网络来降低参考态和衰减态的相对相移。由于当  $V_{\rm C}$  处于高电平时,电路处于衰减状态。 $V_{\rm CN}$ 处于高电平时,电路处于衰减状态。

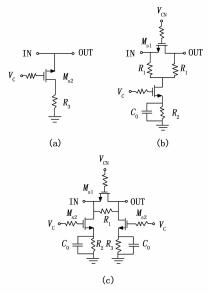

### 1.6 MOS 管开关优化设计

开关型衰减器的性能取决于 MOS 管开关的性能。为了确保衰减器的高线性度以及高动态范围,要求 MOS 管开关有较好的隔离度以及线性度<sup>[24-26]</sup>。与化合物工艺相比,CMOS 工艺的 MOS 管开关电子迁移率较低、寄生电容较大,这将导致较大的导通电阻和较大的到地寄生电容,从而引起射频信号的泄露<sup>[13]</sup>。由于本设计中衰减器工作频率较高,MOS 管的寄生电容是导致插入损耗增大的主要因素。因此,本文在满足衰减精度的同时,针对 MOS 管开关进行了优化设计以降低插入损耗。

NMOS 晶体管在工作时需要调节栅极电压使 MOS 管在 线性区和截止区之间切换使得漏极和源极导通。通过改变 栅极电压来实现 MOS 管导通和关断功能。NMOS 管在导通 时等效为电阻阻值和栅极电压的关系为:

$$R_{\rm on} = \frac{1}{\left\lceil \mu_{\rm n} C_{\rm n} \frac{W}{L} (V_{\rm gs} - V_{\rm TH}) \right\rceil} \tag{11}$$

其中:  $V_{gs}$ 是栅极电压,  $V_{TH}$ 是阈值电压,  $u_n$  和  $C_n$  是使用工艺常量, W 是 NMOS 晶体管的总宽度, L 是总长度。

当晶体管在工作时,NMOS 管的栅极电压一般在1.2 V和 0 V之间变化,所以栅极电压和阈值电压的差值可以看成一个常数。我们通过改变 NMOS 管的长宽比可以改变 NMOS 管的导通电阻。实际设计中,取总长度 L 为60 nm,通过改变 NMOS 管的宽度和插指数来改变 NMOS 管的总宽度。但是栅极和源极、漏极之间的寄生电容与宽度成正比:

$$C_{gs} = C_{gd} = 0.5 \ WLC_n$$

(12)

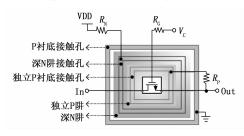

图 5 所示为带有寄生电容的 NMOS 场效应管模型图。 其中, $C_{\rm gs}$ 为 MOS 管栅极和源极之间寄生电容, $C_{\rm gd}$ 为栅极和源极之间寄生电容, $C_{\rm gb}$ 为栅极和衬底之间的寄生电容, $C_{\rm db}$ 为漏极和衬底之间的寄生电容。

图 5 NMOS 开关寄生电容模型

为了减小栅漏电容  $C_{sd}$ 和栅源电容  $C_{ss}$ 的影响,在 MOS 管的栅极和控制电压之间串联大电阻  $R_G$ 。该电阻不仅增加了开关的线性度,还可降低导通电阻相对于输入信号电平变化而产生的变化。为减少  $C_{db}$ 带来的射频信号泄漏,可以将衬底通过电阻  $R_P$  连接到源极,同时将深势阱通过一个偏置大电阻  $R_N$  连接到电源,如图 6 所示。 MOS 管栅极级而控制电压为 1.2 V 的  $V_C$  控制 MOS 管的通断。 DNW 端接 1.2 V 的电源端形成反向 PN 结,利用 PN 结正向导通反向截止的特性降低信号的泄露并且防止信号的互相耦合。

图 6 添加偏置电阻的 NMOS 管结构

以 8 dB 衰减位为例,图 7 给出了 NMOS 开关管在采用了偏置电阻与不采用偏置电阻情况下插入损耗的对比。由图 7 可知,未加偏置电阻的电路插入损耗在 2 dB 左右,通过增加偏置电阻可以看到电路的插入损耗在 1 dB 左右。

图 7 优化前后插入损耗对比

可以看到随着频率的升高,增加偏置电阻后的 MOS 结构降低插入损耗的效果越来越好,优化后比优化前插入损耗每一位都降低了 0.4 dB 以上,级联后的整体电路插入损耗降低了 2.4 dB 以上。

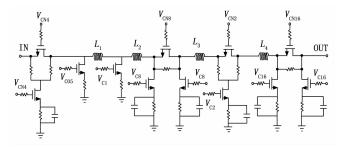

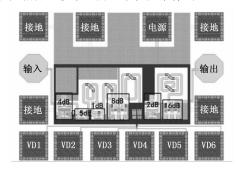

#### 1.7 整体电路设计

整个六位数控衰减器电路由前述 6 个衰减位级联而成。针对衰减器的线性、负载效应和功率处理能力调整衰减位的级联顺序[27]。6 个衰减位级联一共有 64 种顺序,不同的级联方式对整体电路影响较大,为降低各衰减位级间阻抗失配对性能的影响,首先将两个衰减位级联,在衰减位之间连接电感以吸收寄生电容的影响,在加入下一衰减位时要选择一个对整体性能影响最小的排序。一般在级联时,要将端口驻波性能好的衰减位放在两端并且要避免相同拓扑结构的衰减单元相邻,从而优化整体性能。最终得到的 6位数控衰减器按照 4 dB、0.5 dB、1 dB、8 dB、2 dB、16 dB的顺序级联组成,其整体电路原理图如图 8 所示。其中  $V_{\text{COS}}$ ;  $V_{\text{CI}}$ ;  $V_{\text{CS}}$ ;  $V_{\text{CI}}$ ;  $V_{\text{CNS}}$ ;  $V_{\text{CIS}}$ ;  $V_{\text{CIS}}$ ,  $V_{\text{CNS}}$ ;  $V_{\text{CNS}}$ ;  $V_{\text{CNS}}$ ;  $V_{\text{CIS}}$ ,  $V_{\text{CNS}}$ ;  $V_{\text{CIS}}$ ,  $V_{\text{CNS}}$ ;  $V_{\text{CN$

图 8 衰减器电路

# 2 版图设计以及仿真分析

基于 55 nm CMOS 工艺完成了该数控衰减器的设计及 仿真,该工艺有十一层基本金属层,采用 M1 金属层作为接 地层,为了防止信号之间的串扰,所以采用大面积铺地的 方式,但工艺要求 M1 金属宽度要在  $12~\mu m$  以内,本次设计的金属采取  $2~\mu m$  正方形中间裁取  $1~\mu m$  正方形的方式来进行大面积通铺,具体图案如图 9~ m 所示。 M2 层金属作为电源层来传输控制信号, M2 金属层要求宽度在  $12~\mu m$  以内,所以与 M1 金属层采取一样的方式来通铺。此外,采用 TM2 金属层作为射频传输层来保证版图满足工艺加工要求。为了尽可能缩小核心电路面积,级联电感的设计采取 TM1 与 TM2 两层金属来设计。

图 9 通铺基本结构

并且为了满足级联需求,本次设计中的电感均为自行 建模设计,并未采用工艺库中的电感。

整体版图如图 10 所示,核心电路面积仅为 0.36 mm× 0.16 mm (不包括焊盘)。其中最外侧设置焊盘,左右两侧放置 GSG 来作为信号输入和输出端口。底部放置控制信号焊盘,并且在控制焊盘与各个衰减位之间增加二级反相器,保证各个衰减位都有一对反相控制信号输入,二级反相器不仅可以保证一对反向信号还可以减少控制电压焊盘个数。由于二级反相器比较小,所以未在图中标出。

图 10 整体版图设计

使用 Cadence 仿真工具对版图进行电磁仿真,由于 Cadence 仿真工具只能对无源器件进行仿真,所以在进行电磁 仿真时先将 MOS 管和电阻器件去掉,进行整体的电磁仿真,提取 S参数后,在与 MOS 管和电阻级联得到最后的仿真结果。

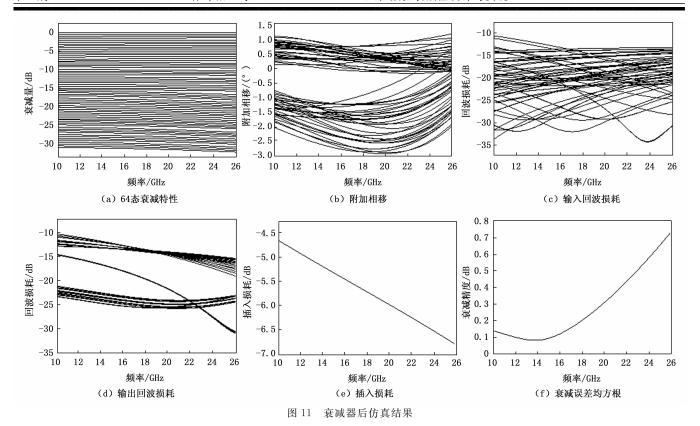

在 10~26 GHz 频率范围内,后仿真结果表示衰减量随 频率变化的曲线如图 11 (a) 所示,由衰减曲线看出,衰减器具有良好的衰减平坦度。由图中可以看到在小衰减量时,衰减曲线线性度很高。随着衰减量的增大,衰减误差开始逐渐变大,在衰减量 16 dB 时衰减曲线线性度变化明显。随

着频率的增加,大衰减量时电路同时工作的 MOS 管数量增大,导致在插入损耗增大的同时影响了衰减精度。

在各衰减态下,附加相移随频率变化曲线如图 11 (b) 所示,由图可知,在  $10\sim26$  GHz 频率范围内,各衰减态的附加相移小于 $\pm3^\circ$ ,具有非常优异的相位性能。如表 1 所示,与其他文献所设计的衰减器相比,本文设计的衰减器附加相移精度提高了 20%以上。

图 11 (c) 和图 11 (d) 所示为分别为各衰减态的输入 回波和输出回波。在各衰减态的回波损耗均小于一10 dB, 有利于前后级电路的级联。与表 1 中其他文献相比,本文 设计的衰减器输入输出回波损耗处于平均水平。

由图 11 (e) 和图 11 (f) 可知,衰减器的损耗和衰减误差均方根分别小于一7 dB 和 0.8 dB。由图 11 (e) 可知,衰减器参考态的插损损耗在一4.7~一6.7 dB 之间,优于表1 中其他文献设计的衰减器。随着频率的升高,衰减器的插入损耗逐渐增大,这是由于随着频率的升高,MOS 管的导通电阻对信号的衰减逐渐增大。

表 1 本文设计与其他文献设计对比

| 文献       | [14]   | [15]   | [16]   | 本文      |

|----------|--------|--------|--------|---------|

| 频率/Hz    | 8∼12 G | 0∼21 G | 8∼12 G | 10∼26 G |

| 最大衰减/dB  | 31.5   | 31.5   | 31.5   | 31.5    |

| 插入损耗/ dB | <8.7   | <11.5  | <9.3   | < 6.7   |

| 附加相移/(°) | <3.5   | <4.38  | <12    | <3      |

| 回波损耗/dB  | <-11   | < 8.35 | <-10   | <-10    |

# 3 结束语

本文设计了一种低插入损耗、低附加相移的 CMOS 数控衰减器。该衰减器针对不同衰减单元选择合适的拓扑结构,针对 MOS 开关导通电阻和寄生电容所导致的插入损耗,采用了悬浮栅和悬浮衬底连接结构,并采用电容补偿网络和电感补偿网络以降低附加相移。针对不同衰减单元级联阻抗失配问题,采用串联电感的方式来优化衰减器性能。该数控衰减器基于 55 nm CMOS 工艺进行了设计及版图仿真。仿真结果表明,在 10~26 GHz 频率范围内,插入损耗小于一7 dB,附加相移小于土3°,衰减误差均方根小于 0.8 dB,核心电路面积仅为 0.36×0.16 mm²(不包括焊盘)。

# 参考文献:

- [1] 段云芳. 60 GHz 射频衰减器的研究与设计 [D]. 南京: 东南大学, 2017.

- [2] 秦 昌. GaAs 微波开关与衰减器研究与设计 [D]. 成都: 电子科技大学,2019.

- [3] 高 军,曹祥玉,张 广,等. 一种波束赋形相控阵天线的分析与设计[J]. 西安电子科技大学学报,2008,35(6):1084-1088.

- [4] 杨漫菲. 基于 SiGe BiCMOS 工艺的 Ku 波段收发前端芯片研究与设计 [D]. 成都: 电子科技大学, 2017.

- [5] 徐 蕾. K 波段 6 位 MMIC 数字移相器与衰减器的设计 [D]. 西安: 西安电子科技大学, 2019.

- [6] 周赡成. Ku 波段 MMIC 数控移相器和数控衰减器的研究与设计 [D]. 杭州: 浙江工业大学, 2019.

(下转第300页)