文章编号:1671-4598(2023)07-0077-08

DOI: 10. 16526/j. cnki. 11-4762/tp. 2023. 07. 012

中图分类号:TJ01

文献标识码:A

# 集成电路综合自动测试系统硬件平台设计

冯建呈,王占这,闫丽琴,殷 晔,尉晚惠,王红字,吴朝华

(北京航天测控技术有限公司,北京 100041)

摘要:针对当前国内集成电路产业快速发展的现状,通过分析集成电路测试需求,研制了国产超大规模集成电路综合自动测试系统硬件平台;首先设计了基于 PXIe 总线的硬件平台总体架构方案,其次研制了包含数字测试模块等高性能 PXIe 测试仪器,进一步构建了测试头等分系统并完成系统集成,采用高性能外部仪器和自检校准分系统,对硬件平台进行了指标测试;基于BM3110MPB 开展了测试验证;验证结果表明,硬件平台数字测试单通道最高测试速率为 1 600 Mbps、DPS 可实现最大输出电压 12 V、最大输出电流 800 mA,具备连接性测试、功能测试、直流参数与交流参数测试等功能;该硬件平台未来可有效满足国产超大规模集成电路测试需要。

关键词:集成电路测试;自动测试系统; PXIe 总线; 数字测试;测试头

# Hardware Platform Design of Integrated Circuit Automatic Test System

FENG Jiancheng, WANG Zhanxuan, YAN Liqin, YIN Ye, WEI Xiaohui, WANG Hongyu, WU Zhaohua

(Beijng Aerospace Measurement and Control technology Co. , Ltd. , Beijing 100041 , China)

Abstract: In view of the rapid development of domestic integrated circuit (IC) industry, an integrated automatic test system hardware platform for very large scale integration circuit (VLSI) based on the requirement of IC testing was developed. Firstly, the overall architecture scheme of the hardware platform based on PXIe bus was designed. Secondly, the high-performance PXIe test instruments including the digital test modules were developed, the testing sub-system was further constructed, and the system integration was completed, the subsystem of high-performance external instrument, self-checking and calibration was used to test the hardware platform, and the test and verification based on BM3110MPB chip were carried out. The test verification results show that the single channel maximum rate of the hardware platform digital test is 1 600 Mbps, the device power supply (DPS) can achieve the maximum output voltage of 12 V and maximum output current of 800 mA, the system has the test functions of the connectivity, function, direct current (DC) parameters and alternating current (AC) parameters. The hardware platform can effectively meet the needs of domestic VLSI testing in the future.

Keywords: IC test; automatic test system; PXIe Bus; digital test; tester head

## 0 引言

测试在集成电路的设计、生产、筛选等环节中占有重要地位,是保证集成电路良率的重要手段[1-3]。集成电路的测试内容主要包含直流参数测试、交流参数测试、功能测试三类。其中直流参数测试项目一般包含输入高/低电平电压、输出高/低电平电流、输入高/低电平电流、静态电源电流、动态电源电流等测试,交流参数是指时间类的参数,如传输延迟时间等。功能测试如CPU、DSP等的功能测试,主要按照芯片的设计规定,给被测器件输入管脚施加相应的激励信号,按照周期、器件引脚检测输出管脚的响应,并将检测到的输出管脚响应与期望响应进行比较,判断电路是否存在故障[1-7]。

完成集成电路的测试,主要采用集成电路测试系统。 受限于国内集成电路测试设备的水平,目前国内集成电路 特别是超大规模集成电路的测试主要采用国外进口设备, 如美国泰瑞达公司的 J750 系列、Ultra Flex、日本爱德万公司的 V93000 以及 NI 公司的 STS 测试系统等<sup>[8-12]</sup>。

上述测试系统一般采用总线架构、集成测试仪器构造成测试设备,在上位机程序的控制下完成测试。以应用广泛的 V93000 为例,其硬件系统分为五部分:测试头、主控计算机、配电控制机柜、支撑体和液冷系统。测试头是系统的核心,实现被测集成电路测试矢量的收发与比较,测试头内部包含如测试仪器机笼,各类型测试仪器安装在机笼中,典型的测试仪器类型包含数字通道板、DPS 板、模拟测试板等,其中数字通道板最高测试速率可达 1.6 Gbps [13-15]。相比较而言,国产集成电路测试设备的测试速率较低,一般在 200 MHz 以下,主要应用在中小规模数字集成电路、模拟电路和混合信号电路测试中,基本不能满足 FP-GA、CPU、DSP 等典型国产超大规模集成电路的测试需求。

针对当前国内集成电路产业快速发展的现状,为进一

收稿日期:2022-04-21; 修回日期:2023-03-27。

作者简介: 冯建呈(1982-), 男, 山东济宁, 硕士, 高级工程师, 主要从事集成电路测试方向的研究。

引用格式: 冯建呈, 王占选, 闫丽琴, 等. 集成电路综合自动测试系统硬件平台设计[J]. 计算机测量与控制, 2023, 31(7): 77-84.

步提升国产高性能集成电路测试设备水平、满足产量不断 提升的高性能国产集成电路设计验证、量产测试等测试需 求,研制国产超大规模集成电路综合自动测试系统,未来 可有效满足国产超大规模集成电路测试需要。

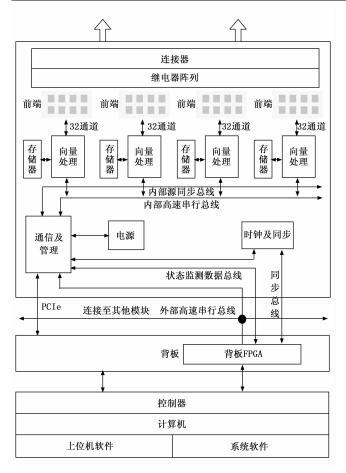

#### 系统总体设计

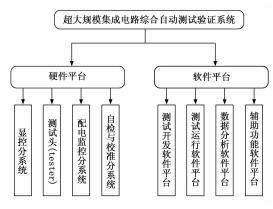

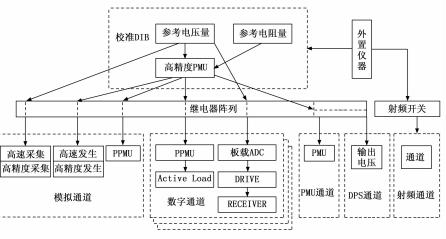

超大规模集成电路综合自动测试验证系统主要包含硬 件平台、软件平台。硬件平台作为基础支撑平台,提供被 测试集成电路所需的硬件测试资源。软件平台作为实现测 试验证的基础软件环境,具备开发运行、数据分析、状态 监测、硬件管理等功能。超大规模集成电路综合测试验证 系统总体组成框图如图 1 所示。

图 1 系统总体组成图

硬件平台包含测试头、配电监控分系统、显控分系统、 自检校准分系统等四部分。具体组成如图 2 所示。

图 2 硬件平台基本组成框图

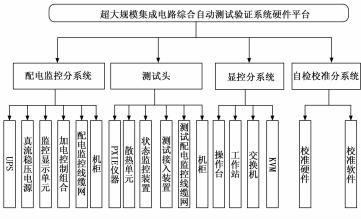

#### 1.1 显控分系统

主要包含主控工作站、矢量转换工作站、网络设备等; 主控工作站部署自动测试软件, 矢量转换工作站部署矢量 转换软件,显控分系统内部通过 LAN 网络实现互联;主控 工作站通过适配卡与 PXIE 仪器连接,实现仪器的控制信息 和数据信息交互,通过 LAN、GPIB 等接口控制外挂式 仪器。

#### 1.2 测试头

主要包含基于 PXIe 总线的测试仪器等。测试头通过

PXIe 总线外挂式控制器连接主控工作站的适配卡, 基于 PXIe 总线接收控制信息、上传测试数据信息; PXIe 总线背 板接收各模块的温湿度、用电信息等;状态监控单元采集 测试头其他部分的运行状态信息并将信息上传到配电监控 分系统;测试头内所有的硬件资源汇集到 DIB 接口板,通 过接口板完成与被测芯片的测试接入适配功能。

# 1.3 配电监控分系统

配电单元:外部供电分成两路,一路用于液冷单元供 电,另一路接入稳压配电单元,进行稳压和AC/DC转换, 分别用于显控分系统、测试头等供电;

监控显示单元:实现 AC/DC 电源的输出监测、测试头 内部状态监控信息读取、PXIE 背板数据读取,并实现上述 信息的显示、本地存储和报警功能; 根据主控计算机的查 询等指令,实现基于 LAN 的数据上传功能。

#### 1.4 自检校准分系统

主要包含外部校准仪器、内部校准仪器和自检校准 DIB 等。仪器通过 LAN/GPIB 等与主控工作站相连, 自检校准 DIB 通过 RS485 与主控工作站相连。测试头中的仪器、校 准仪器和 DIB 均在自检校准软件的控制下,配合完成自检 校准。各分系统组成与接口关联如图 3 所示。

# 2 主要测试仪器设计方案

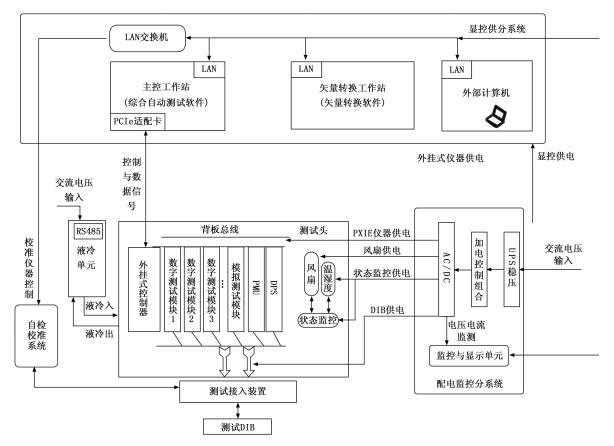

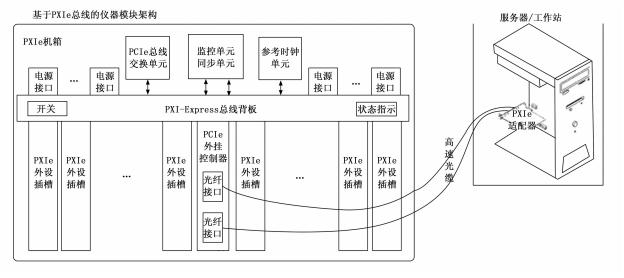

# 2.1 基于 PXIe 总线的硬件仪器架构方案

测试仪器部分由工作站、PXIe 外挂控制器及 PCIe 适配 卡、背板及各功能模块组成,工作站与背板通过 PXIe 外挂 控制器及 PCIe 适配卡通信,系统背板通过 PCIe 交换芯片

和控制器的下行链路与各功能模块进行通信。主要实现 工作站与数字测试模块、模拟测试模块、DPS等模块的 通信、控制和管理协调,实现功能模块的时钟分配、同 步、互联通信以及功能模块状态监测,实现芯片功能、 直流参数等的测试,组成框架如图 4 所示。

# 2.2 数字模块设计方案

数字测试模块主要用于芯片数字通道的直流参数、 交流参数和功能测试。数字测试模块通道数量多,具有 动态负载和 PPMU 功能,可以实现芯片多个数字管脚的 漏电流、导通电阻、阈值电压等直流参数的测量。

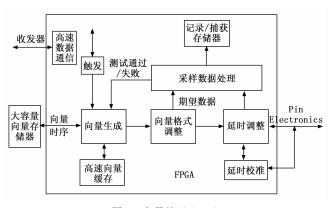

数字测试模块包含软件和硬件两部分。软件运行在 计算机上,主要实现基本控制和测量功能。软件生成的 指令和数据与数字测试模块硬件之间通过控制器模块、 背板传输,这些数据在通信及管理单元中进行解析和分 配,再通过内部高速串行总线或内部源同步总线与每个 向量处理单元通信。数字测试模块的主要工作原理如图 5 所示。

背板有专用的同步总线,模块内的时钟及同步单元使 用该总线实现多个模块之间的同步。通信及管理单元将控 制指令和数据发送到每个向量处理单元,每个向量处理单 元控制 32 个通道。输入/输出信号经由前端电路、继电器 阵列和连接器与测试头的探针连接。

背板 FPGA 和通信及管理 FPGA 之间还有外部高速串

图 3 硬件平台分系统接口关系

图 4 基于 PXIe 总线硬件仪器框架

行总线和状态监测总线连接。其中外部高速串行总线用于 以广播方式分发大量控制数据。状态监测数据总线则用于 传输状态监测数据,该类数据具有非常高的优先级,必须 使用独立的总线。

#### 2.2.1 FPGA 固件设计方案

通信及管理 FPGA 主要实现数字测试模块与计算机之间的数据交互,实现数字测试模块之间以及数字测试模块

和其他模块之间的同步,实现数字测试模块的电源管理、 任务管理等。

向量处理 FPGA 主要实现向量生成、向量及时序数据读写、向量格式调整、采样数据处理、向量延时调整、延时校准、前端芯片控制等功能,均通过 FPGA 实现,每 32 通道由一个 FPGA 处理。向量处理是数字测试模块的核心,向量处理 FPGA 的功能框图如图 6 所示。

图 5 数字测试模块硬件工作原理图

图 6 向量处理 FPGA

测试向量全部存储在大容量向量存储器中,工作启动前将部分需要执行循环、跳转等复杂命令的向量通过向量存储器控制器加载至高速向量缓存。而其他不需要执行上述复杂指令的向量则在运行时动态、顺序的从存储器中读出,通过FPGA内部的向量缓冲FIFO,由向量生成单元读取并处理。

#### 2.2.2 高速数字信号发生与采样方案

前端电路将逻辑信号转换为特定电压值的模拟信号, 也能将端口的模拟信号按照一定的阈值转换为逻辑信号, 其信号通过率大于 1.6 Gbps 即可满足要求。在上述硬件基础上,还需要通过向量处理 FPGA 实现高速数字信号的发生和采样,即生成最高 1.6 Gbps 的前端电路控制信号;需要实现高速数字信号采样,以最高 1.6 GHz 的频率采样前端电路转换后的数字信号。本设计中采用 FPGA 内部的专用 ISERDES 和 OSERDES 电路实现逻辑信号的采样和发送。在 FPGA 内部,数据流以并行形式存在,所以可在较低频率下进行处理。处理后的数据可以通过 OSERDES 电路电化输出。ISERDES 电路的工作过程和 OSERDES 电路电化输出。ISERDES 电路的工作过程和 OSERDES 相反,实现将高速采样的逻辑信号转换为 FPGA 内部的低速并行信号。使用上述电路可以实现 1.6 Gbps 的 IO,更重要的是,使用该电路可以同时支持时序边沿的调整。在 FPGA本地,使用较低频率的时钟就可以对并行数据进行编码,从而改变串化后的数据。尽管对并行数据进行实时编码的难度很大,但该方法具有以下优点:

- 1) 作为 FPGA 内置电路,稳定性好和一致性高,不需要额外的外围器件:

- 2)FPGA 的每个 IO 管脚均有专用的 I/O SERDES,可以支持大量的 IO;

- 3) FPGA 内部的数据均为多位并行数据,使数据格式调整功能的实现成为可能。

#### 2.2.3 多通道同步方案

在实现时钟、触发同步和通道延时校准的基础上,可以实现多通道同步,满足大规模数字电路测试需求。

由于需要大范围可调的时钟频率,且时钟相位关系固定,所以使用具有多芯片同步功能的 DDS。设计需要保证 3种时钟(SYNCCLK、PCLK、SCLK),共 48 路时钟具有严格相位关系。普通时钟缓冲器可以保证片内信号的延时一致性,但是多数无法保证芯片间的一致性。为保证时钟同步,所有时钟均在背板生成,然后分配到每个模块。

在实现时钟同步的基础上,可以实现触发同步。模块间、模块与控制计算机之间的触发和信息交互都基于一个同步的低频时钟(SYNCCLK)。该低频时钟与每个模块的工作时钟都有严格的相位关系。每个模块都有4对差分信号线连接到背板FPGA,其中两对用于模块向背板FPGA发送信号,两对用于背板FPGA向模块发送信号。由于参考时钟的频率较低(10 MHz或以下),所以不需要源同步时钟。背板FPGA时钟使用参考时钟的下降沿工作,模块使用参考时钟的上升沿工作,可以为布线留下足够的余量。信号传输延时控制在±5~10 ns 就可以满足同步要求。

上述同步总线可以实现各个模块在低频同步时钟域(SYNCCLK)同步,关键步骤是实现低频同步时钟域的信号转换到模块工作时钟(PCLK)域后,各个模块之间的同步。时钟分频、时钟分配电路使用的缓冲器都具备芯片间同步和输出延时调整功能,可以保证 SYNCCLK 和 PCLK之间具有固定的、可重复的相位关系,从而实现工作频率相同时,各模块间的同步。

## 2.2.4 通道延时校准方案

延时校准主要功能是通过测量数字测试模块输入/输出通道的内部延时,以及传输线、设备接口板走线等外部延时,然后调整每个通道内部的延时值,使所有信号从模块到被测对象的传输和从被测对象到模块的传输分别同步。校准过程包括数字测试模块内部各通道输出/输入延时校准和外部延时校准两个步骤。

内部输出/输入对齐借助校准设备接口板进行,校准设备接口板主要为继电器阵列,数字模块各通道可通过继电器阵列切换,从而测量两个通道间相对的输入/输出延时偏差。

具体延时信息含义如下:

- 1) 内部发送延时 A: 参考通道的 FPGA 发送信号至前端电路的走线延时、前端芯片的发送传播延时;

- 2) 内部接收延时 B: 参考通道的 FPGA 接收信号至前端电路的走线延时、前端芯片的接收传播延时;

- 3) 内部发送延时 C: 被测通道的 FPGA 发送信号至前端电路的走线延时、前端芯片的发送传播延时;

- 4) 内部接收延时 D: 被测通道的 FPGA 接收信号至前端电路的走线延时、前端芯片的接收传播延时;

- 5) 外部走线传播延时 E: 参考通道的前端芯片至校准 DIB上的继电器之间的走线及线缆的传播延时;

- 6) 外部走线传播延时 F: 被测通道的前端芯片至校准 DIB 上的继电器之间的走线及线缆的传播延时;

首先选择一个通道为参考通道与一个被测通道,利用各通道的自发自收,参考通道与被测通道的互发互收,分别可以测得参考通道自发自收时间 T1,被测通道的自发自收时间 T2,参考通道发接收通道收的时间 T3,被测通道发参考通道收的时间 T4。

由上述参数可以计算出,参考通道与被测通道发送延时相对偏差,接收延时相对偏差。偏差为负,则表示被测通道发送或接收延时大于参考通道,偏差为正,则表示被测通道发送或接收延时小于参考通道。通过切换被测通道,分别测出各通道相对于参考通道的延时偏差。

在测得的发送延时偏差与接收延时偏差中分别找到最小值,此值表示相对于参考通道延时最大偏差,所有通道均通过 FPGA 内部延时补偿对齐该通道,从而实现各通道输入/输出对齐。

内部输出/输入对齐主要是将数字模块内部前端电路与 FPGA之间的输出延时与输入延时对齐,而外部延时补偿 则是通过 TDR 技术测量前端电路与被测芯片之间的延时 (走线延时、线缆延时)等参数,实现整体延时补偿。

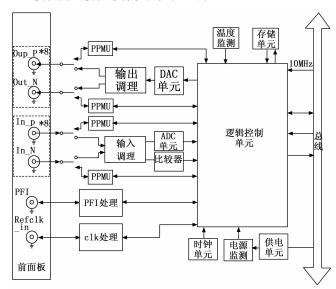

#### 2.3 模拟模块设计方案

模拟测试模块需要实现任意波形发生器、数字化仪功能,对外输入输出端口共有 32 个 (16 差分输出/16 差分输入),每个端口均支持 PPMU 功能,快速实现直流参数测量功能。主要包括 DAC、ADC、输入调理、输出调理、PP-MU、FPGA 控制、存储控制、供电单元、电源监测及温度监测等几部分。

具体工作原理:用户通过程序配置通道的功能模式:

1)信号发生时,用户通过 PXIe 总线将波形数据下载至存储器,通过上位机驱动程序配置波形参数,输出使能后,波形输出至端口连接器;2)信号采集时,用户通过上位机驱动程序配置采集参数,采集使能后,通过总线将采集数据读入至上位机,上位机进行数据处理后,显示相关参数信息;3) PPMU 测量时,用户通过上位机配置 PPMU 的工作模式,驱动 DAC 激励输出及 ADC 采集,实现直流参数测量。

模拟测试模块总体框图如图 7 所示。

图 7 模拟测试模块原理框图

#### 2.3.1 逻辑控制单元

该单元实现了整机的通讯、系统控制、逻辑功能控制及数据处理功能。硬件主要由 FPGA 芯片、配置芯片以及必要外围电阻电容等组成。FPGA 包含数据处理及各种功能控制逻辑,实现整机的总线通讯、系统控制及功能控制。

# 2.3.2 输出调理

输出调理电路实现输出信号的各种调理功能,对输出信号的幅频特性起到决定性作用。主要由 I-V 转换、滤波器组、衰减电路、单端转差分电路、功率放大电路及其他辅助电路组成。

输出调理流程: DAC 转换后的波形信号输入运放电路,将差分电流信号转换为单端电压信号。该信号输入至滤波器组,滤波后的主信号输入初级放大,然后信号经由衰减电路、直流叠加电路及单端转差分电路,实现信号的基础调理,转换生成的差分信号输入至两组功率放大电路,实现双端口单端/差分信号输出。

滤波器组:主要包含3个低通滤波器:高分辨率信号发生采用1kHz及40kHz进行信号滤波处理,高采样率信号发生采用100MHz滤波器进行信号滤波处理,且两种信号发生滤波器均可实现旁路控制,滤波器切换采用高频继电器实现。多截止频率滤波器的设计可有效提升全频带输

出信号的信号质量。

衰减电路: 为充分保证信号的幅度分辨率, 衰减电路 设计参考对标模块,以3dB步进设计衰减电路,组合叠加 实现 0~18 dB 衰减,等效实现信号输出电路 7 个输出量程。 2.3.3 输入调理

输入调理电路实现输入信号的各种调理功能,主要由 阻抗选择电路、耦合选择电路、单端/差分电路、量程选择 电路、偏置 DAC 及其他辅助电路组成。

输入调理流程:输入信号通过 50  $\Omega/1$  M $\Omega$  阻抗选择, 根据耦合方式选择 AC/DC 耦合,根据单端/差分采集模式, 选择差分转单端电路单元工作路由,转换后的信号经由量 程控制电路实现幅度调制并叠加直流偏置信号, 经多截止 频率滤波器组后输入至 ADC 单元。多截止频率滤波器组的 设计可有效提升输入的 THD 及 SFDR 指标。ADC 单元根 据当前通道的采集模式(高速/高分辨率)程控选择 ADC。

滤波器组:主要包含3个低通滤波器,高分辨率信号 发生采用 1 kHz 及 40 kHz 进行信号滤波处理, 高采样率信 号发生采用 100 MHz 滤波器进行信号滤波处理, 且两种信 号采集模式中滤波器均可实现旁路控制,滤波器切换采用 高频继电器实现。

衰减电路: 为了充分保证信号的幅度分辨率, 衰减电 路设计参考对标模块,以 3 dB 步进设计衰减电路,组合叠 加实现 0~18 dB 衰减,等效实现信号 7 个输入量程控制。

#### 2.4 器件供电单元 (DPS) 模块设计方案

DPS模块主要实现对被测集成电路的供电、补偿和回 采。DPS 模块由电源激励模块(Force)、接收模块 (Sense)、低噪声放大器、保护电路等组成。

为保证测试数据的精度,输出电源信号采用多级放大 方式,并采用高性能滤波设计,共有8个电源通道。各组 成单元如下:

控制 FPGA 接收来自计算机的命令和数据,并根据这 些命令和数据,控制板上的所有其它电路。DPS 电源给小

电流 DPS 通道的功率放大器提供电源。 DPS 模数和数模转换器用于设定输出电 压或者电流, 以及采集转换输出的电压 和电流。DPS 通道用于设定输出电压, 通过负反馈实现电压稳定, 以及测量电 流等功能。

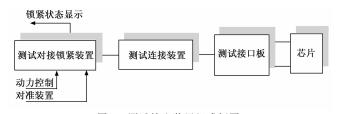

# 3 测试系统集成与校准方案

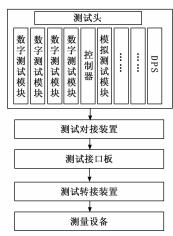

# 3.1 测试系统集成方案

测试头是测试系统的核心单元。测 试头集成安装 PXIe 总线仪器模块、液冷 内循环单元、测试接入装置、风冷单元、 监控单元、线缆网等。其中,测试接入 装置包含测试头对接锁紧装置、测试接 口板动力对接装置、测试接口板(含测 试插座)组成,通过测试连接装置实现

测试头硬件资源通道与测试接口板的资源信号转接,通过 测试插座实现对多类型集成电路的测试安装。测试接入装 置组成如图 8 所示。

图 8 测试接入装置组成框图

测试接入装置安装在测试头顶端, 其下部通过线缆与测 试头内部的测试仪器连接、转接到其内部安装的弹性连接器 上。同时其内部还安装有动力结构件,实现安装在测试接入 装置顶端的测试接口板(DIB)下压与弹性连接器相连。

## 3.2 校准方案[16-20]

硬件平台的校准主要分为两个步骤,外部校准以及内 部校准,以内部校准为主。整体校准结构如图 9 所示。

硬件平台通过专用的校准 DIB 板实现各仪器模块的统 一校准。校准 DIB 板上放置有参考电压源,参考电阻以及 高精度 PMU 单元。具体校准时,首先通过外部校准仪器对 校准 DIB 板上的内部校准资源进行校准,然后通过内部校 准资源对仪器通道的各项参量进行测量,实现各通道的自 动校准。无论是内部校准还是外部校准,校准过程中,都 会记录被校准参量的预期值与实际值,由此得到需要被修 正的偏差, 在校准完成后会以文本的格式保存于上位机中, 在具体测试时,软件会首先加载校准文本数据,用以修正 系统误差。

## 4 硬件平台指标测试验证

#### 4.1 硬件平台技术指标测试

在完成硬件平台集成工作后,采用高性能外部仪器、 测试接口板、测试线缆相结合的方式,对硬件平台的技术 指标进行了测试。测试时的连接框图如图 10 所示。

通过测试,主要指标满足指标要求,测试数据如下:

图 9 校准结构示意图

图 10 测试平台测试项设备连接图

表 1 硬件平台测试指标

| 模块类型   | 指标类型                                                                                                                    | 测试数据                                                                                                                                                     |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 数字测试模块 | 通用指标                                                                                                                    | 通道数:128<br>测试向量存储器:256 M/通道<br>捕获记录存储器:4 K<br>最大外部输入信号电压:-1.5~6.5 V                                                                                      |  |  |  |  |

|        | 时序指标                                                                                                                    | 向量周期范围:5 ns~10 μs<br>驱动边沿数量:4<br>比较边沿数量:2                                                                                                                |  |  |  |  |

|        | 输出                                                                                                                      | 交流特性:最小摆幅: $200 \text{ mV}$ ;最大摆幅: $8 \text{ V}$ ;最小脉冲宽度: $750 \text{ ps}@1 \text{ V}$ 摆幅 直流特性: 电压范围: $-1.5 \sim 6.5 \text{ V}$ ;最大电流: $40 \text{ mA}$ ; |  |  |  |  |

|        | 输入                                                                                                                      | 最小可检测脉冲宽度: $750 \text{ ps}$ ; 输入电压和比较阈值范围: $-1.5\sim6.5 \text{ V}$ ; 比较阈值数: $2(双门限比较)$ ; 最大电流: $40 \text{ mA}$ ;                                         |  |  |  |  |

|        | PPMU                                                                                                                    | 电压范围: - 2.0~6.5 V;<br>电流档位: ± 40 mA、± 1 mA、± 100 μA、<br>±10 μA、±2 μA;                                                                                    |  |  |  |  |

| 模拟测试模块 | 音频信号 测试                                                                                                                 | 通道数:16;<br>分辨率:24 bit;<br>信号发生采样率:102.4 KSps;<br>信号采集采样:102.4 KSps;                                                                                      |  |  |  |  |

|        | 基带信号<br>测试                                                                                                              | 通道数:16;<br>分辨率:16 bit;<br>信号发生采样率:400 MSps;<br>信号采集采样率:256 MSps;                                                                                         |  |  |  |  |

|        | DC 参数<br>测量                                                                                                             | 通道数:32;<br>信号发生采样率:192 KSps<br>信号采集采样率:192 KSps                                                                                                          |  |  |  |  |

| DPS    | 通道数:8<br>电压输出范围:0~12 V;<br>电压设定分辨率:10 mV;<br>电压设定精度:误差 ≤ 0.5%FS;<br>最大输出电流:800 mA;<br>电压测量范围:0~12 V<br>电流测量范围:0~800 mA; |                                                                                                                                                          |  |  |  |  |

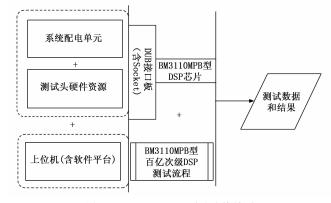

#### 4.2 基于典型芯片的测试验证

选取的典型芯片 BM3110MPB 兼容 SPARC V8 体系结构的 32 位微处理器,采用 BGA484 封装形式,含 64 路通用 IO。BM3110MPB集成多路模拟量与开关量数据采集、多路模拟与数字信号输出、外设接口,内部通过总线将高性能 CPU、浮点处理器、模拟开关、计数器、定时器、通用 I/O、输出等功能模块集成在单一芯片上,适合测试、实时计算以及控制领域应用。该芯片基于先进架构,包含典型的外设接口,输入输出引脚数量较多,工作频率较高,具有较好的典型性,适合验证所设计综合自动测试验证系统的功能指标。

首先,需要设计 BM3110MPB 测试接口板,实现综合自动测试验证系统与 BM3110MPB 的连接。BM3110MPB 测试连接关系如图 11 所示。

图 11 BM3110MPB 测试连接关系

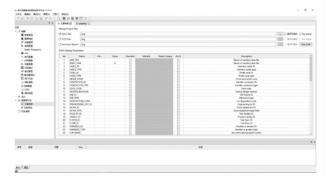

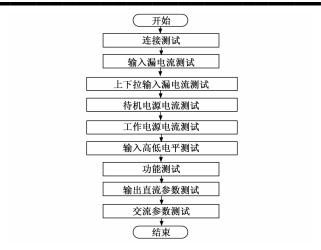

其次,在综合自动测试验证系统上位机软件配置芯片 BM3110MPB测试流程。参照 BM3110MPB的产品使用手 册,测试流程包含连接测试、输入漏电流测试、上下拉输 入漏电流测试、电源电流测试、输入高电平测试、输出直 流参数测试、交流参数测试等。该芯片的测试程序截图如 图 12 所示。

图 12 BM3110MPB 测试程序截图

测试程序流程图组成如图 13 所示。

最后,编译、下载所开发的测试程序,执行该测试程序,实现该芯片的详细测试。将测试数据与 BM3110MPB 的产品使用手册中相关参数对比,验证系统测试能力。测

图 13 BM3110MPB 测试程序流程图组成

试程序执行时长不超过 1 分钟,表 2 为运行 BM3110MPB 芯片的测试程序的结果。

表 2 BM3110MPB 电路测试结果

| —————————————————————————————————————— |     |     |         |    |    |  |  |  |

|----------------------------------------|-----|-----|---------|----|----|--|--|--|

| 参数                                     | 最小  | 最大  | 测试值     | 单位 | 结论 |  |  |  |

| 输出高电平电压 VOH                            | 2.4 | _   | 2.997   | V  | 合格 |  |  |  |

| 输出低电平电压 VOL                            | _   | 0.4 | 0.292   | V  | 合格 |  |  |  |

| 输入高电平电压 VIH                            | 2.0 | _   | 2.0     | V  | 合格 |  |  |  |

| 输入低电平电压 VIL                            | _   | 0.8 | 0.8     | V  | 合格 |  |  |  |

| 输入高电平漏电流 IIH                           | _   | 1   | 0.500   | μΑ | 合格 |  |  |  |

| 上拉输入高电平漏电流 IHPU                        | _   | 5   | 3.749   | μΑ | 合格 |  |  |  |

| 下拉输人高电平漏电流 IHPD                        | 20  | 200 | 179.716 | μΑ | 合格 |  |  |  |

| 输入低电平漏电流 IIL                           | _   | 1   | 0.503   | μΑ | 合格 |  |  |  |

| 上拉输人低电平漏电流 IILPU                       | 20  | 200 | 179.85  | μΑ | 合格 |  |  |  |

| 下拉输人低电平漏电流 IILPD                       | _   | 5   | 3.889   | μΑ | 合格 |  |  |  |

| 待机电源电流 IDDD(SB)                        | _   | 5   | 0       | mA | 合格 |  |  |  |

| 付机电源电流 IDDD(SB)                        | _   | 5   | 4.171   | mA | 合格 |  |  |  |

| 动态电流 IDD(dy)                           | _   | 166 | 79.523  | mA | 合格 |  |  |  |

| Pll 旁路情况 Sdclk 输出延时                    | _   | 8   | 1.2     | ns | 合格 |  |  |  |

| oen 输出延时                               |     | 10  | 7.5     | ns | 合格 |  |  |  |

| writen 输出延时                            | _   | 10  | 6.5     | ns | 合格 |  |  |  |

测试结果表明,综合自动测试验证系统经过参数校准后,测试效率、测试数据能够满足 BM3110MPB 芯片的测试需求,该集成电路综合自动测试系统硬件平台设计合理可行。

## 5 结束语

本文主要介绍了国产超大规模集成电路综合自动测试系统硬件平台。硬件平台作为基础支撑平台,提供被测试集成电路所需的硬件测试资源,包含测试头、配电监控分系统、显控分系统、自检校准分系统等四部分,其中测试头是硬件平台的核心单元。通过依次完成测试头内部的核心测试仪器研制、系统集成与指标测试、基于典型芯片的测试验证等工作,表明硬件平台最高可实现 2048 数字通道、单通道最高测试速率 1 600 Mbps 等数字测试指标、实

现电压输出范围 0~12 V、最大输出电流 800 mA 等 DPS 测试指标等。该系统目前已经通过了国产典型芯片如 CPU、DSP、FPGA、SRAM 等的初步测试验证,未来进一步优化系统软硬件后,可广泛应用在集成电路的设计验证、量产测试和筛选测试等环节,满足国产集成电路测试需要。

#### 参考文献:

- [1] 郑永丰,张贵恒,董 阳,等. 国产芯片自动测试系统射频测 试模块设计 [J]. 计算机测量与控制. 2019, 27 (10): 41-49.

- [2] 李 丹. 中国集成电路测试设备市场概况及预测 [J]. 电子产品世界, 2019 (10): 4-7.

- [3] 罗宏伟,刘竞升,余永涛,等.超大规模集成电路测试现状及关键技术[J].电子产品环境可靠性与试验,2021,39(2):16-20.

- [4] 王 柱. 数字集成电路测试技术应用分析 [J]. 科技创新与应用, 2020 (12): 148-149.

- [5] 徐琛玥. 数字集成电路测试技术应用分析 [J]. 集成电路应用, 2020, 37 (9): 8-9.

- [6] 严梓扬, 苏成悦, 张宏鑫. Vhdl 在数字集成电路设计中的应用分析 [J]. 自动化与仪器仪表, 2017 (5): 131-133.

- [7] 张建文. 基于 ARM 的数字集成电路测试系统的研究 [J]. 中国新技术新产品,2018 (9):21-22.

- [8] 罗 斌. 基于 ATE 的高端图像传感器芯片测试技术 [J]. 集成电路应用, 2019 (8): 66-68.

- [9] 唐 丽, 邹映涛, 唐 昱, 等. 基于 V93000ATE 的随机数采集检测方法 [J]. 电子测试, 2019 (24): 32-34.

- [10] NING Z H, HELENIAN. A low drift curvature-compensated bandgap reference with trimming resistive circuit [J]. Journal of Zhejiang University-SCIENCEC: Computers & Electronics, 2011, 12 (8): 698-706.

- [11] 王 颖. 爱德万: 让自动测试贯穿一切 [J]. 中国电子商情 (基础电子), 2018 (9), 22-24.

- [12] 单祥茹. 爱德万测试 PS1600: 物联网应用的最佳选择 [J]. 中国电子商情(基础电子), 2015(9): 47-48.

- [13] 赵 桦, 王建超. 基于 V93000ATE 的大电流测试方法研究 [J]. 电子与封装, 2017, 17 (12): 14-17.

- [14] 王喜莲. 爱德万测试 AVI64 扩充 V93000 平台对智能器件的 测试能力 [J]. 中国集成电路, 2016, 25 (4): 80-84.

- [15] 叶 雷. 爱德万测试 V93000 和 T2000 [J]. 电子产品世界, 2015, 22 (10): 77-78.

- [16] 郝叶军. 数字集成电路测试仪测试通道电路设计 [D]. 成都: 电子科技大学, 2011.

- [17] 王耀国,王 酣. J750 型 SOC 测试系统校准技术概述 [J]. 工业计量, 2011, 21 (2): 31-33.

- [18] 李 飞. IC 测试仪数字通道板设计及同步技术研究 [D]. 成都: 电子科技大学, 2018.

- [19] 纪明霞, 周志刚, 王翠珍, 等. IC 测试仪通用校准设备的研究 [J]. 仪表技术, 2015 (3): 8-10, 49.

- [20] 董锁利, 丁 颖, 张建兰. IC 测试仪的校准与设计策略 [J]. 工业计量, 2013, 23 (1): 66-68.