文章编号:1671-4598(2021)01-0246-05

DOI: 10. 16526/j. cnki. 11-4762/tp. 2021. 01. 050

中图分类号:TN919

文献标识码:A

# 基于 MAX10 的多通道小型化记录仪设计

朱志斌<sup>1,2</sup>、马游春<sup>1,2</sup>、鲍爱达<sup>1,2</sup>

(1. 中北大学 电子测试技术国家重点实验室,太原 030051;

2. 中北大学 仪器科学与动态测试教育部重点实验室,太原 030051)

摘要:针对记录仪小型化的要求,设计了一种基于 MAX10 的多通道小型化记录仪; MAX10 是一块内部集成了多通道 AD 采集功能 FPGA 控制芯片,所以相比传统的数据记录仪少了单独的 AD 转换芯片以及众多模拟开关,与普通搭载了外部 AD 的记录仪相比,体积缩小了接近四分之一;并且实现八路采集,采样频率为 1 MHz,分辨率为 4096;为了应用在一些恶劣环境下,选择用 SD 卡作为存储设备,存储容量为 32GB;若系统被撞击损毁,只需要取出 SD 卡,依然能方便回收采集的数据;经过测试,记录仪的 8 个通道均能正常采集数据,而且在系统采集数据期间,猛烈撞击装置破坏了电路板后,将 SD 卡取出,依然能有效回收采集的数据。

关键词:数据采集; MAX10; 小型化; 双启动; 多通道; SD卡

# Design of Multichannel Minimized Recorder Based on MAX10

Zhu Zhibin<sup>1,2</sup>, Ma Youchun<sup>1,2</sup>, Bao Aida<sup>1,2</sup>

- (1. State Key Laboratory for Electronic Measurement Technology, North University of China, Taiyuan 030051 China; 2. Ministerial Key Laboratory of Instrument Science & Dynamic Measurement, North University of China,

- Taiyuan 030051, China)

Abstract: Aiming at the requirement of miniaturization of recorder, a miniaturization recorder based on MAX10 is designed. MAX10 is a kind of FPGA which integrates the function of AD acquisition. So this recorder works without extra AD conversion chip and many analog switches comparing with the traditional data recorder. Compared with ordinary recorders equipped with external AD, the volume is reduced by nearly a quarter. Eight—channel sampling is realized with a sampling frequency of 1MHz and a resolution of 4096. In order to be used in some harsh environments, the SD card is selected as the storage device. The storage capacity is 32 GB. If the system is damaged by impact, only the SD card needs to be taken out, and the collected data can still be easily recovered. After testing, the eight channels of the recorder can collect data normally, During the data collection of the system, when the circuit board was destroyed because of the violent impact, the collected data can still be effectively recovered. by taking out the SD card.

Keywords: data acquisition; MAX10; miniaturization; dual boot; multichannel; SD

## 0 引言

随着科技的发展,生产生活中需要测量的参数越来越多<sup>[1]</sup>,尤其在航天、军事以及精密设备等领域,数据采集测量的要求更加苛刻,对设备体积,功耗,采样通道数量等各项指标提出新要求<sup>[2]</sup>,在一些航天军事应用方面,有时还要面临一些极端环境条件。这些需求使得人们不断探索改进采集存储设备。市面上多路采集存储的实现方案通常是单片机等控制器控制外部搭载的 AD 转换芯片以及众多模拟开关,存储部分常使用 flash 完成。然而这种通用方案在一些场合有很大局限性<sup>[3]</sup>。比如需要将记录仪内嵌在设备中,而且要求记录仪在外力作用下损毁后,依然能方便回收采集的数据,这样就对记录仪的体积与数据防护方面

提出了更高的要求。

针对这些要求,设计一种基于 MAX10 的多通道记录仪。MAX10 是一款 Altera 公司小外形封装的 FPGA,集成数模转换模块,与单片机作为主控相比,FPGA 具有工作延时少,编程方便灵活,计算速度更快等优点<sup>[4]</sup>,同时,MAX10 支持双配置功能,本设计将采集存储功能作为一个单独程序下载配置进 MAX10 中,将读取数据功能作为第二个功能程序也下载配置进 MAX10 中,上电启动采集存储程序,当工作完毕时候,改变控制引脚电平,让 MAX10 启动数据读取程序,读取 SD 卡中的数据传输到上位机中。这样可以很大程度利用 FPGA 逻辑资源。若记录仪损毁,则从记录仪残骸中取出 SD卡,再进行数据回收。

收稿日期:2020-05-20; 修回日期:2020-06-09。

基金项目:国防科技重点实验室基金(6142001180412)。

作者简介:朱志斌(1994-),男,湖北孝感人,硕士研究生,主要从事数据采集方向的研究。

马游春(1977-),男,江苏盐城人,博士,副教授,硕士生导师,主要从事高速数据采集与存储系统方向的研究。

鲍爱达(1980-),男,河北秦皇岛人,在读博士,副教授,硕士生导师,主要从事无线通信方向的研究。

引用格式:朱志斌,马游春,鲍爱达. 基于 MAX10 的多通道小型化记录仪设计[J]. 计算机测量与控制,2021,29(1):246-250.

## 1 系统结构及原理

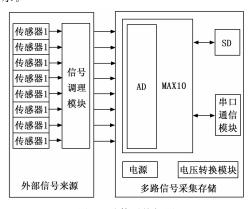

本设计主要为多路信号采集存储模块,信号来源部分是由外部产生,不作为本设计研究部分。多路信号采集存储模块包括内嵌 AD 的 MAX10 主控模块、SD 卡存储模块、电源与电压转换模块以及串口通信模块。总体系统框图如图 1 所示。

图 1 总体系统框图

上电后,MAX10 开始配置内部 AD 的相关参数,并设置中断。外部多路信号过来后,通过转换接到 MAX10 上,内部 AD 采集开始工作,然后 MAX10 将采集的多路数据提取出来,加上帧头帧尾,进行混合编帧,然后将帧数据写入缓存,当缓存达到 512 字节后,写入 SD 卡⑤。采集结束后,转换控制引脚电平状态,使 MAX10 启动第二套程序,从 SD 卡读取数据,然后将数据通过串口发送到上位机,进行观察验证采集的数据帧。根据每一帧的相应位来判断区分哪些采集的数据分别属于哪一路。

## 2 系统硬件电路设计

## 2.1 主控与 AD 模块

主控与 AD 采集模块均是 MAX10,它只需要单电源供电,封装方式为 EQFP144,在启动速度、功耗以及安全性方面有着很大的优势。成功在低成本、单芯片小外形封装的 FPGA 器件中完成了先进的数据处理功能,还包含了以前版本同系列器件的特点,在集成功能与集成密度方面有更大加强,其密度范围在 2 k 至 50 KLE 之间。在非易失集成器件领域,有着极大地进步<sup>[6]</sup>。

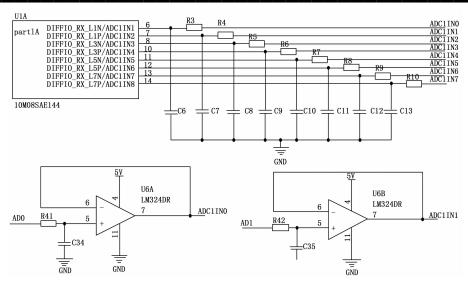

其集成功能包括模数转换器(ADC)和双配置闪存,支持在一个芯片上存储两个镜像,在镜像间动态切换。FP-GA将 AD 采集功能作为 IP 核,具体为 Altera Modular ADC Core,MAX10 内部集成的 ADC 模块具有 12bit 精度,并且最多可以支持到 17 个 ADC 输入采样通道。其中,MAX10 的 ADC 是 1 MHz 逐次逼近型寄存器(SAR)模数转换器。采集电路如图 3 所示。此外,MAX10 还支持 Nios II 嵌入式操作系统,可以直接配置成一个基本的片上操作系统,简化繁琐的各种通信协议与存储模块的构建,适合一些对处理速度要求不高、功能简单的应用场合,能够大

幅缩短开发周期<sup>[7]</sup>。MAX10 同时还具备休眠模式,当系统一段时间不工作时候,设置 MAX10 进入休眠模式,可以极大降低功耗,延长电池的使用时长,这对嵌入式设备而言,是一个非常实用的功能。

#### 2.2 存储模块

通用的存储数据方法有 U 盘、存储卡以及 Flash 等方式。然而,一般的 Flash 存储容量较小,大容量的 Flash 尺寸也会相应增加<sup>[8]</sup>,与小型化设计目标有冲突,而且也不便回收。U 盘体积更大,而且与其它部件连接处不够稳固。而 SD 卡存储容量大、体积小、价格低廉,通信连线数量少、读写速度快。使用与回收都非常方便。在本设计背景条件下,这些优点使得 SD 卡非常适合作为此次设计的存储方式。而且在一些试验环境危险的条件下,整个记录装置可能损毁,而此时,SD 卡能轻易从损毁的装置里面取出,不易损失采集的数据,故本设计存储器选择 SD 卡。

本设计选用的 SD 卡类型为 SDHC,它采用 SD2.0 协议规范,存储容量为 32 GB,可以配置选择工作在 SDIO 模式或者 SPI 模式,此次设计选择 SPI 模式,所以共用到 CS、CLK、MISO、MOSI 四根信号线,在 SPI 模式下采用 1 位数据位宽,单纯衡量 SD 卡数据传输速度,理论上能够达到50 Mbps 的读写速率,远大于本设计的采集所需。

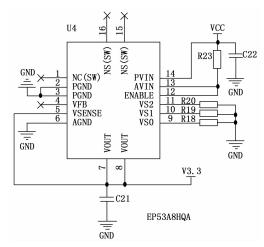

#### 2.3 电压转换模块

本设计使用的 MAX10 芯片是单电源型号。所以我们使用的电源芯片是 ALTERA 公司的 Enpirion 电源转换芯片 EP53A8HQA,原理连接图如图 2 所示。它属于 DCDC,16 引脚封装,其输出最大电流 1A。其尺寸为:长 3.0 mm、宽 3.0 mm、高 1.1 mm。工作温度范围在 $-40\sim105$  C之间,从芯片尺寸以及各种参数性能上考虑,EP53A8HQA非常适合作为本设计的电压转换芯片。

图 2 电源转换芯片原理图

#### 2.4 串口通信模块

模块选用 Silicon Labs CP2102GM 的 USB-UART 芯片,能实现 USB 转 UART 串口功能[9],芯片内部集成了

图 3 八路采集连接图

1024字节 EEPROM,可以用来存储各类信息。支持波特率区间为在 300 bps 至 1 Mbps,工作温度范围为—40 至+85度,支持对外供电:5 V或 3.3 V。在 USB 部分,符合 USB2.0 规范。可以用一根 USB 线将它连接到上 PC 的 USB 口进行串口数据通信。也可作为供电接口,使用十分简易方便。

## 3 系统软件设计

为了有效利用 FPGA 内部资源,同时借助于 MAX10 独有的双启动配置功能,本设计将整个软件系统划分为采集存储部分与读取发送部分,系统运行哪一套程序取决于BOOT\_SEL 引脚的高低电平。当数据采集结束,已经将数据写入 SD 卡,再改变 BOOT\_SEL 引脚的电平,使MAX10 运行读数与发送程序。FPGA 根据内部时序逻辑,向外围电路发送各种控制命令[10]。外部的八路信号进来后,启动 MAX10 内部的 AD采集功能,然后将八路数据提取出来,加上帧头帧尾,再将帧数据写入缓存中,当达到了 SD卡写的最小单元 512 个字节时,将 FIFO 中的数据提取出来,按时序写入 SD卡中。采集结束后,改变 BOOT\_SEL引脚电平,让 MAX10 运行 SD卡读程序,读取 SD卡数据,然后通过串口发送到上位机。

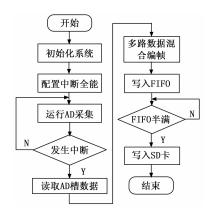

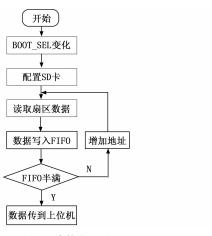

#### 3.1 采集存储软件设计

如图 4 所示,上电初始化 SD 卡,使得 SD 卡工作在 SPI 工作模式下,校准 AD, 配置中断使能寄存器,开启采集中断功能,然后启动 AD 采集,开始等待数据采集完成时产生的中断,当检测到中断发生,读取 AD 各路采集槽数据,然后 在 数据 两端加上 帧头 0xFFFFFF01 帧尾0xFFFFFFFF,进行混合编帧,再将这一帧数据写入 FIFO中,当 FIFO 半满时候,将 FIFO 中数据读取出来,然后写入 SD 卡中,完成数据的采集存储功能。如果 FIFO 没有达到半满就继续等待 AD 采集过来的数据[111]。

图 4 采集存储图

#### 3.2 读取与发送软件设计

如图 5 所示,当 FPGA 上 BOOT \_ SEL 引脚电平发生了转换,FPGA 会启动下载配置的第二程序,运行 SD 卡数据读取与发送程序,MAX10 配置 SD 卡到预定工作模式后,开始进入读数阶段,先将地址写入写入单个命令块CMD17,然后按位发送读命令,将 SD 卡单个扇区数据读取出来,之后,将数据写入缓存,当缓存达到半满,取出缓存的数据,然后串口发送出来,到上位机上显示。当缓存中的数据发送完成后,改变 SD 卡读数地址,再次启动 SD 卡读数流程,将下一个扇区地址内的数据读取出来,依次循环往复,直到采集的数据都被读出,最终在串口助手上显示出采集的帧数据。通过这种方式,可以很方便地分析一帧中各位的数据,然后对比每一路作为测试的电压值,相互对比验证。

#### 4 系统测试与实验结果

# 4.1 SignalTap 在线逻辑分析仪

Signal Tap 是第二代系统级在线调试工具,它可以选择多个需要观察的目标信号以及选择目标信号的捕获方

图 5 读数发送图

式<sup>[12]</sup>,而传统的外部逻辑分析仪测试时候需要外部连线,当要测试信号多达数十个时候,传统外部逻辑分析仪就有很大的局限性,所以,相比较而言,Signal Tap 不需要物理接线,更容易测试更多数量的信号,极大地方便了开发调试过程。

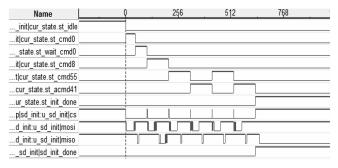

SD卡的读写操作都是基于命令的,通过向 SD卡发送相应的命令,获得相应的基本底层驱动接口程序。如图 6 所示,用在线逻辑分析仪捕获信号变化,可以看出在 SD卡空闲状态标志拉低后,SD卡片选信号 cs 拉低,开始初始化配置过程,系统依序进入 st\_cmd0、st\_wait\_cmd0、st\_cmd8 st\_cmd55、sta—acmd41 等状态,在这些状态下,mosi分别发送了 cmd0、cmd8、cmd55、acmd41 等一系列初始化命令,SD卡的 miso 引脚在一些命令状态过程中做出了一系列响应,最后 sd\_init\_done 信号被拉高,证明 SD卡已经初始化成功。

图 6 SD 初始化图

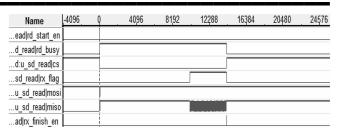

如图 7 所示,从在线逻辑分析仪中可以看出当 rd\_start\_en 脉冲来临后,rd\_busy 信号被拉高,标志系统进入了 SD 卡读取数据状态,与此同时,片选信号拉低,使得 SD 卡能够有效通信。还可以看到,rx\_flag 信号拉高期间 miso 数据线上电平不断在跳转,mosi 则维持在高电平,说明 miso 处在传输过程中,MAX10 正在读取 SD 卡存储的数据。读数结束后,rx\_finish\_en 产生一个高脉冲,表示一个单元的数据读取完毕。

图 7 SD 读数图

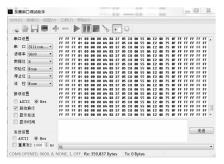

## 4.2 读取的数据

本设计将每一路采集数据都用 16 位数据格式表示,其中低 12 位存储采集的数据,高 4 位用 0 填充。将 SD 卡存储的数据读出后,用串口形式发送出来,在串口助手上观察八路采集的结果。从图 8 可以看到,串口助手接收到的数据帧头为 0xFFFFFFF01,帧尾为 0xFFFFFFFF。每组数据前的 0 是程序中额外添加的,用来分割每组数据。去掉用 0 填充的高四位之后,八组采集的十六进制数据分别为0x000、0x0A4、0x337、0x5C0、0x855、0xAE2、0xD75、0xFFF。

图 8 接收数据图

ADC 测量范围在 0 V 到 2.5 V 之间,模拟输入量程从 000h 到 FFF 之间,它的分辨率为  $2^{12}$  = 4 096,1 LSB = 2.5 V/4 096 = 610.35  $\mu$ V。其中,实验测试中作为输入的八路 数据采集口电压分别为 0 V、0.1 V、0.5 V、0.9 V、1.3 V、1.7 V、2.1 V、2.5 V,从理论上分析,八路分别对应 的采集的原始值分别为 0x000、0x0A4、0x333、0x5C2、0x851、0xAE1、0xD70、0xFFF。但是由于作为实验输入 的数字电源的电压有一定误差干扰,输出的电压值与实验的理论值有所偏差,使得 MAX10 采集得到的帧数据与理论电压值不完全相同,有一定的偏差。但是从数据结果来看,与预期值非常接近,属于可以接受的实验误差范围。所以此次实验结果符合预期。

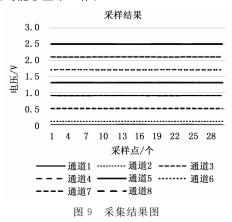

为了更加明显直观地观察比较采集的结果是否正确,从众多采集点中选取中间 30 组采集的十六进制原始数据,再经过转换变成对应电压值,然后绘制成折线图,图中有八条不同线型的线,它们分别代表着 8 个通道采集的数据转化后的电压值。如图 9 所示,可以很清楚看到八路数据采集分别在 0 V、0.1 V、0.5 V、0.9 V、1.3 V、1.7 V、2.1 V、2.5 V附近以一个非常微小的幅度上下震荡,这些

数据结果与实验的八路输入电压非常接近,证明此记录仪 八路采集均能够正常工作。

## 5 结束语

为了解决记录仪小型化问题,本文设计了一种基于MAX10 的多通道小型化记录仪,能同时采集八路信号,由于采用了具备 AD 采集功能的 MAX10 作为在主控芯片,和外加 AD 方案的记录仪相比,缩小了近四分之一的体积。并且实现了八路采集,采样频率为 1 MHz,分辨率为4 096。同时,为了应用在一些恶劣环境下,例如在炮弹参数测试实验中,当炮弹落地,发生强烈撞击后,要求保存飞行过程中采集的参数。所以本设计发生选择用 SD 卡作为存储设备,其存储容量为 32 GB,易于回收数据。而且系统易于升级改进,由于 MAX10 的采集通道多达 17 个,可以根据各使用场合选用合适的采集通道数量。存储部分也可以更换更大容量的 SD 卡以便记录更多数据,经过实测,在设备工作期间,摔击记录仪设备能准确有效得采集 0 V 至 2.5 V 之间的信号。能够满足设计要求。在需要将记录仪嵌入进设备的应用场合,应用前景十分广阔。

本设计由于时间原因,也存在着一些不足之处,例如 在将 SD 卡内部数据读取出来发送到上位机的过程中,选用 的是简单的串口传输,这种方式传数比较慢,今后可以做一下改进,换成 USB 直接传出到上位机中,而不是使用 UART 转 USB 方式。

### 参考文献:

- [1] 郑 瑞,肖顺文,王 涌,等. 基于 FPGA 的多通道数据采集与多速率发送系统设计[J]. 数字技术与应用,2020,38 (1):118-120.

- [2] 易志强,韩 宾,鲜 龙,等. 旋转环境下基于 FPGA 的多通 道数据采集系统设计 [J]. 电子技术应用, 2019, 45 (9): 60-64.

- [3] 丁红晖. 基于 PGA900 的海温及压力采集系统研究与设计 [D]. 太原: 中北大学, 2018.

- [4] 李锦明, 刘梦欣, 成乃朋, 等. 基于 FPGA 的多路无线数据采集系统设计 [J]. 中国测试, 2019, 45 (12): 102-105.

- [5] 王 丹,姚 磊,杨云川,等.基于FAT文件系统的高速大数据记录仪的设计[J].电子设计工程,2019,27(20):75-78.

- [6] 卫建华,高 燚,邓云兵. 基于 MAX10 的多路 PWM 控制系统研究 [J]. 电子设计工程, 2016, 24 (14): 139-142.

- [7] 焦新泉,翟 菲,刘东海,等. 高精度温度采编设备的稳定性优化设计[J]. 兵器装备工程学报,2019,41(2):140-142.

- [8] 张 吉. 一种多路数据采集模块的硬件设计 [J]. 电子技术, 2016, (6): 52-55.

- [9] 徐 良,张 博. 基于 CP2102/CP2103 的接口转换为 USB 接口的应用设计 [J]. 国外电子元器件, 2008, 16 (5): 15-17, 21.

- [10] 郑 佳. 多通道数据记录装置的设计与实现 [D]. 太原:中北大学,2013.

- [11] 徐文艳. 高速高精度流水线逐次逼近模数转换器的研究与设计 [D]. 北京: 北京交通大学, 2016.

- [12] 耿三钧. 基于 FPGA 的多平台虚拟仪器研究设计 [D]. 武汉:武汉理工大学,2009.

。2011. (上接第 245 页)

产具有现实的支撑意义。该评价系统也可以无缝进人各种 产品的生产线中,实现产品生产过程的在线无损检测,使 得整条生产线实现闭环控制,提高生产效率、降低损耗、 降低生产成本和管理成本。

#### 参考文献:

- [1] 任晓可,李 健. 电磁超声技术在钢板缺陷检测中的研究 [D]. 天津: 天津大学, 2008.

- [2] 苏州博昇科技有限公司,一种金属基复合材料脱粘检测方法 [Z]. 2017.

- [3] 魏 鑫. Matlab r2018a 从入门到精通 [M]. 北京: 电子工业 出版社, 2019.

- [4] 李国厚. 导电结构涡流/超声检测与评估技术的研究 [D]. 杭

- [5] Edward B. Magrab Shapour Azam. MATLAB 原理与工程应用第 2 版 [M]. 北京: 电子工业出版社, 2006.

- [6]李 敏,罗洪艳,郑小林,等.一种改进的最大类间方差图像分割法[J].南京理工大学学报(自然科学版),2012,36(2);332-337.

- [7] 孙建成,曾培峰,禹素萍,等.二值图像的区域标识与噪声去除[J].天津工业大学学报,2006,25(1):45-47.

- [8] 邓仕超, 黄 寅. 二值图像膨胀腐蚀的快速算法 [J]. 计算机工程与应用, 2017, 53 (5): 207-211.

- [9] 高敬鹏, 江志烨, 赵 娜. 机器学习: 基于 OpenCV 和 Python 的智能图像处理 [M]. 北京: 机械工业出版社, 2020.

- [10] 石鑫华. 基于 Vision Assistant 的图像处理实用教程 [Z]. 2013.