文章编号:1671-4598(2020)06-0086-04

DOI:10.16526/j. cnki.11-4762/tp. 2020.06.018

中图分类号: TP391.41

文献标识码:A

# 基于 CPLD 芯片的视频图像码率控制方法研究

# 陈建国、康海静、兰 英

(成都理工大学 工程技术学院,四川 乐山 614000)

摘要:针对小波视频码率控制方法缓冲器容量有限,存在控制精准误差大的问题,提出了基于 CPLD 芯片的视频图像码率控制方法研究;依据基于 CPLD 芯片的视频图像码率控制框图可知,该码率控制方法是由 CPLD 芯片视频图像灰度增强、编码码率控制、视频质量控制与主动跳帧控制 4 个模块组成;运用 Philips 公司的 9 位视频输入处理器 sAA7113 芯片解码视频,输出达到 ITU656 标准的 YUV 4:2:2 格式的数字视频信号;统一视频信号格式,利用灰度的线性变换的方式增强图像灰度,借助 Verilog HDL 描述 CPLD 执行算法;依据固定编码比特率和固定图像质量之间关系,获取编码特性,并计算缓冲区和编码帧目标比特数,依据当前渲染到纹理值,统计报文丢失率,由此实现视频图像编码码率控制;为了扩充缓冲器容量,对视频质量和主动跳帧进行控制,使缓存满度的减小不会导致控制器无法精准调节后续帧量化参数;由实验结果可知,该方法最小控制误差为 0.07,能够有效提高视频质量。

关键词: CPLD 芯片; 视频图像; 码率; 控制

# Research on Video Image Bit Rate Control Method Based on CPLD Chip

Chen Jianguo, Kang Haijing, Lan Ying

(Engineering & Technical College, Chengdu University of Technology, Leshan 614000, China)

Abstract: Aiming at the problem of the limited buffer capacity of the wavelet video bit rate control method and the large control accuracy error, a method of video image bit rate control based on the CPLD chip is proposed. According to the CPLD chip—based video image bit rate control block diagram, it can be known that the code rate control method is composed of CPLD chip video image gray level enhancement, encoding bit rate control, video quality control, and active frame skip control. Use Philips 9—bit video input processor sAA7113 chip to decode video and output digital video signals in YUV 4:2:2 format up to ITU656 standard. Unify the video signal format, use the linear transformation of gray to enhance the gray of the image, and describe the CPLD execution algorithm with the help of Verilog HDL. According to the relationship between the fixed encoding bit rate and the fixed image quality, the encoding characteristics are obtained, and the target bit number of the buffer and the encoding frame is calculated. According to the current rendering to the texture value, the message loss rate is counted, thereby implementing the video image encoding bit rate control. In order to expand the buffer capacity, the video quality and active frame skip are controlled so that the reduction of the buffer fullness will not cause the controller to accurately adjust the quantization parameters of subsequent frames. The experimental results show that the minimum control error of this method is 0.07, which can effectively improve the video quality.

Keywords: CPLD chip; video image; bit rate; control

# 0 引言

在视频应用时,码率控制占据重要地位,保障码率得以约束的前提下,码率控制以提升编码图像的质量水平为目的。为得到更优质的视觉感受,拥有相同的图像质量为视频编码期望特性之一<sup>[11]</sup>。一般情况下,码率控制算法的优化力求帧图像失真度最小,这堪称整体意义上对图像质量进行优化,也许会造成各帧图像内每个宏块的信噪比不集中分布的问题,图像每个部分质量波动很大,导致了主观视觉质量水平降低<sup>[2]</sup>。在目前的视频压缩编码标准中,

收稿日期:2020-04-01; 修回日期:2020-04-15。

基金项目:四川省教育厅科研项目(17ZB0066);成都理工大学工程技术学院院级基金项目(C122017019);成都理工大学工程技术学院教育教学改革项目(2018-JYJG0201)。

作者简介:陈建国(1978-),男,河南孟州人,研究生,讲师,主要 从事混沌保密通信、数字图像处理算法及应用、人工智能算法及应 用等方向的研究。 由于对视频序列中类型不一样的帧采用不一样的编码方式,与此同时,每个帧图像的活动性也不一样,导致每个帧编码后生成的比特数有某些差异<sup>[3]</sup>。

编码速率控制是为了使编码器输出的码流达到稳定,尽可能消除编码端缓冲器溢出问题,进一步提高重建图像质量。过去利用小波视频码率控制方式,该方式可以针对信号执行多分辨分析与时频局部化操作,恢复图像满足人眼的主观需求,借助三维最小度分解原始图像序列,之后借助修改后的等级树集合分区的算法量化效度系数<sup>[4]</sup>。即便此方法有很好的控制效果,但因为交换缓冲器的容量不是无限的,视频码流的突发性有形成拥塞的危险,继而造成丢失缓冲器溢出与信元的后果,传输的服务质量会降低。因此,以 CPLD 芯片为基础的视频图像码率控制方法研究被提出。

# 1 基于 CPLD 芯片的视频图像码率控制

此控制方案利用以 CPLD 芯片的码率为基础的控制方

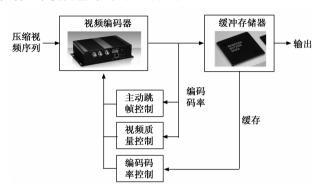

式,借助它的低复杂度、高控制精度达到提高运算速度与控制精度的目的,使当前码率控制算法的性能占据较大优势<sup>[5]</sup>。该控制方案的码率控制方法主要由 CPLD 芯片视频图像灰度增强、视频质量控制、主动跳帧控制和编码码率控制 4 个模块组成,如图 1 所示。

图 1 基于 CPLD 芯片的视频图像码率控制框图

# 1.1 基于 CPLD 芯片视频图像灰度增强

借助视频解码芯片,解码当前的模拟视频信号,并将模拟视频信号转化成数字视频信号,再采用可编程逻辑器件 CPLD,完成灰度线性变换指令,使视频图像的灰度进行增强<sup>[6]</sup>。

#### 1.1.1 视频解码

视频解码芯片采用 9 位视频输入处理器,其型号为 sAA7113,该视频输入处理器来自于 Philips 公司。在系统 中这个芯片的主要功能是使复合视频信号 CVBS 完成 A/D 转换指令,并输出一个数字视频信号在 YUV 4:2:2 格式 中符合 ITU656 标准,即取样频率的两倍(13.5 MHz)行 参考信号  $H_{REF}$ 、场参考信号  $V_{REF}$ 和半像素时钟信号 LLC <sup>[7]</sup>。由于信号钳位、对比度控制、饱和度控制、抗混叠滤波、自动增益控制与亮度控制等能够在视频解码芯片内部完成,因此,只有在系统上电复位后,依据 I<sup>2</sup>C 总线,才能正确地执行视频解码芯片内部相关控制寄存器完成初始化设置,即可获得高质量的数字视频信号和时钟信号,用于同步所有系统<sup>[8]</sup>。

## 1.1.2 视频信号格式统一

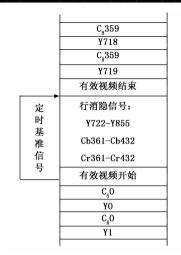

图 2 是一行像素数据的格式。

#### 1.1.3 视频图像灰度增强处理

通过灰度线性变换指令,使视频图像的灰度进行增强, 并利用 Verilog HDL 叙述 CPLD 执行算法。再运用 SAA7113模拟数字转换,输入8位数字视频信号 VPI。在8 位灰度映射表中,选择拨码开关、半像素时钟信号 LLCI 与

图 2 视频信号格式统一

行场同步  $V_{ref}$ 、 $H_{ref}$ ;并将输入的半像素时钟 LLCO 与 8 位数字视频信号 VPO 发送到 sAA7121H 处理器。当每个半像素时钟信号处于上升沿时,判断像素是否处于行程状态或进程状态。如果是,则设定初始为首个进行上下行参考的信号,将偶数位的取样点进行灰度变换,根据波码开关的输入值选择相应的变换函数。在进行灰色映射时,使用case 分支语句将需要处理的灰色映射表和灰度级进行关联。将奇数取样点均设定为 0X80(对应的色差信号为 0),去除颜色信息的同时,对图像进行灰度变换。

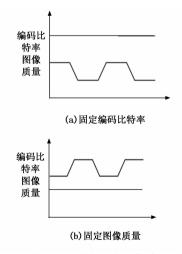

#### 1.2 编码码率控制

在视频编码中,为了达到码率约束要求目的,需利用固定的比特率输出,图像的量化参数会持续变化,图像质量亦会产生波动;为保证质量的均匀,一般情况下利用确定的量化参数图对图像执行量化处理,但是如此输出的编码比特率非恒定不变,在有带宽限制的应用中无法适用。如图 3 所示。

图 3 固定编码比特率与固定图像质量之间关系

在率失真理论的码率控制中,优化策略以码率约束满 足为前提,让全部编码图像的失真度为最小值。因为图像 内容存在差异,在码率固定的前提条件下,每个宏块的量 化参数必然会有波动,造成图像的不同部分质量产生波动,对主观视觉质量造成影响。考虑到以上两种编码方法(获取固定码率的编码方法与获取一致的编码质量的编码方法的特性),所以,一种码率控制方法被提出了:码率约束达到要求后,最小化每个宏块量化参数的方差。借助此种优化方式,能够让宏块量化参数分布更为集中,近似于量化参数固定编码方式,进而取得均匀相同的图像质量;与此同时,因为带宽约束得到满足,固定码率的编码方式亦可以应用于带宽受限的应用环境中。确保正确解码,每个宏块的量化参数会被执行编码操作并且向解码端传输。

被提出的码率控制以 CPLD 芯片为基础,采用的码率 控制方法先计算目前缓冲区比特数,

$$B = \max_{\{B_{prev} + B'_{prev} - V/p, 0\}}$$

(1)

式(1)中, $B_{prev}$  表示缓冲区域的比特数; $B'_{prev}$  表示上一帧 实际比特数值,V 表示编码速率, $\rho$  表示编码帧率。

依据上述内容,编码帧目标比特数为:

$$B' = V/p - \Delta, \Delta = \begin{cases} B/V, B > \lambda B \\ B - \lambda B, 其他 \end{cases}$$

(2)

式(2)中, λ表示缓冲延迟系数。

提出的基于 CPLD 芯片的视频图像码率控制方法需依据当前渲染到纹理值,统计报文丢失率,结合 CPLD 芯片视频图像灰度增强处理内容,估计报文传输所需的比特数,具体控制步骤如下所示:

Step1: 跳帧控制

统计缓冲区大小,重新计人 EC 编码,以此作为数据 开销:

Step2: 信道状态估计

统计前两帧图像传输反馈的数量,计入纠错报文之中, 由此计算报文出错率;

Step3: 估计需要纠错时间

设置缓冲区图像帧数和报文长度,依据所需发送的报 文总数纠错报文出错率,通过搜索方法计算所需纠错报文 数目;

Step4:确定采用的编码帧分配所需的比特数,将 Step3中得到的渲染到纹理值带人其中,并根据选择的模式 估计纠错报文所需比特数。

依据上述内容,完成编码码率控制。

#### 1.3 视频质量控制

在视频码率控制中,评价控制算法优劣的主要依据为 视频码率,但应用视频码率的同时,还需要对视频质量进 行控制,所以需要引入一个质量控制模块。

# 1.3.1 视频采集

视频采集依靠采集程序与计算机内置的采集卡完成。 档次高的采集卡对应生成高质量视频。某些视频采集卡可 以执行硬压缩,采集速度很快。尽量应用高质量的采集卡 进行视频的捕捉,保证图像效果较好。针对某些可以执行 压缩的采集卡,采集成 AVI 格式视频具有较好效果。进行 采集时,可利用随卡带的采集程序,亦可运用 Premiere 的 采集程序。借助 Premiere 的 cuptu: 命令采集时,需要在模拟信号与 DV 信号中区分出视频信号源,在 cupture format 采集格式中选取 composite (模拟复合)或者是 DV (数字视频)。条件允许的情况下,首选 DV 格式采集。

# 1.3.2 视频编辑

视频作品质量的提高是视频媒体编辑的重要过程,借助对采集压缩后的视频素材执行编辑操作,让视频感染力、表现力增强。编辑过程为:将编辑程序打开,新建视频编辑项目,把数字化的视频素材传输进此项目窗口,对素材进行选择,设置素材在编辑轨上的展开方式,之后调用编辑软件供给的各个软件,比如剪辑、重新排序、衔接素材、添加特效、运动叠加、中英文字幕等。

视频节目编辑成功之后,可以直接压缩成为所需格式,图像信息的损失有效降低,清晰度提高了。使用素材时,最好保持图像的原始尺寸与宽高比。视频片段加入滤镜效果时,需要进行选择,原因是某些滤镜效果会使原视频劣质化,清晰度显著降低,可以决定少加甚至是不加。此外,不超过视频的目标任务的情况下,力求视频压缩的比特率得到提高,图像细节的损失减少。

# 1.4 主动跳帧控制

对于解码器,如果在编码端存在跳帧控制,则解码端将重复前一帧图像的内容,使解码后的重构视频序列满足指定的帧速率。或者可以使用之前编码帧的重建帧,计算通过帧的峰值信噪比。如果第 j 帧被跳过(事实上,没有跳过帧),则使用前一重建帧的第 j-1 帧。如果峰值信噪很小,则说明跳过当前帧并没有显著降低 PSNR,即可得到视频质量没有显著变化,能够作为跳帧控制策略。与一般的跳帧相比,即可作为主动跳帧控件。如果该帧满足主动跳帧的要求,则会生成两种效果:首先是未对帧进行编码,保存一些码字,降低模式判断和运动估计,并减少计算量;其次,缓冲区空间被空出,缓冲区充盈度的减小,将造成控制器无法准确调整后续帧的量化参数。

# 2 实验分析

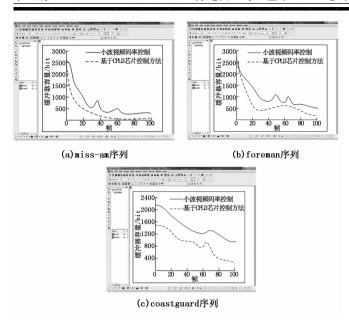

为了验证基于 CPLD 芯片的视频图像码率控制方法的有效性,对标准测试序列(共100帧)进行测试分析,并与小波视频码率控制方法相比较。测试序列为 QCIF 格式,帧频率为20 f/s,以50 kb/s 速率进行编码,缓冲器容量为3500 bit。

在视频图像细节简单情况下,分析不同控制方法下缓冲器所占用量对比分析,结果如图 4 所示。

由图 4 可知,采用小波视频码率控制方法在视频图像变化时,缓冲器占用量较大,而采用基于 CPLD 芯片视频图像码率控制方法缓冲器占用量相对较小。

在视频图像细节丰富情况下,需将视觉图像质量一致性 以帧内失真度均方误差作为度量准则,该误差计算公式为:

$$S = \frac{1}{M} \sum_{i=1}^{M} (S' - \overline{S})^{2}$$

(3)

式中,M 表示视频图像数量; S' 表示重建图像与原图像之间的均方误差; S 越小,失真度就越集中,视频图像也就越清晰。

图 4 不同控制方法下缓冲器所占用量对比分析

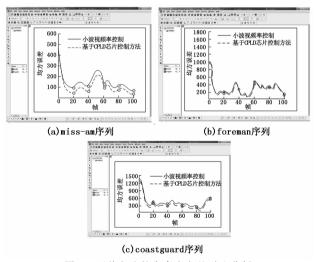

在 miss—am 序列、foreman 序列、coastguard 序列下,将 两种方法的失真度均方误差进行对比分析,结果如图 5 所示。

图 5 两种方法的失真度方差对比分析

由图 5 可知:在 miss—am 序列下,采用小波视频码率 控制方法在帧数为 40~60 帧时,均方误差达到最高为 180;而基于 CPLD 芯片控制方法在该帧数范围内,均方误差达到最高为 270。在 foreman 序列下,采用小波视频码率控制方法在帧数为 60 帧时,均方误差达到最高为 520;而基于 CPLD 芯片控制方法也在 60 帧时,均方误差达到最高为 510。在 coastguard 序列下,采用小波视频码率控制方法在帧数为 100 帧时,均方误差达到最高为 800;而基于 CPLD 芯片控制方法也在 100 帧时,均方误差达到最高为 790。由此可知,采用基于 CPLD 芯片控制方法失真度较小,获取的视频图像更加清晰。

基于上述内容, 统计实际峰值信噪比  $PSNR_Y$ 、 $PSNR_U$ 、 $PSNR_V$  和输出码率大小, 如表 1 所示。

表 1 实际峰值信噪比输出码率大小分析

| 序列           | miss-am | foreman | coastguard |

|--------------|---------|---------|------------|

| $PSNR_Y/dB$  | 38.10   | 39.42   | 41.73      |

| PSNR_U/dB    | 40.91   | 43.16   | 43.20      |

| PSNR_V/dB    | 41.25   | 43.19   | 44.14      |

| 输出码率/kbits/s | 128.03  | 125.07  | 129.15     |

依据表 1 所示实际值,分别采用小波视频码率控制方法(A)和基于 CPLD 芯片控制方法(B)对码率控制精准度进行对比分析,结果如表 2 所示。

表 2 两种方法码率控制精准度对比分析

| 序列         |   | PSNR_Y | PSNR_U | PSNR_V | 输出码率/     |

|------------|---|--------|--------|--------|-----------|

|            |   | /dB    | /dB    | /dB    | (kbits/s) |

| miss-am    | Α | 35.19  | 38.42  | 46.73  | 122.13    |

| miss am    | В | 38.25  | 41.05  | 41.39  | 128.12    |

| foreman -  | Α | 35.82  | 42.15  | 47.39  | 111.12    |

|            | В | 39.40  | 43.22  | 43.40  | 125.18    |

| aanstauned | Α | 40.13  | 44.12  | 42.14  | 120.31    |

| coastguard | В | 41.52  | 43.53  | 44.58  | 129.22    |

$PSNR_Y/dB$  峰值信噪比:采用小波视频码率控制方法在 miss—am 序列下与实际值相差 2.91,在 foreman 序列下与实际值相差 5.09,在 coastguard 序列下与实际值相差 1.12;采用基于 CPLD 芯片控制方法在 miss—am 序列下与实际值相差 0.15,在 foreman 序列下与实际值相差 1.51,在 coastguard 序列下与实际值相差 0.27。

$PSNR_U/dB$  峰值信噪比:采用小波视频码率控制方法在 miss—am 序列下与实际值相差 2.94,在 foreman 序列下与实际值相差 1.01,在 coastguard 序列下与实际值相差 0.93;采用基于 CPLD 芯片控制方法在 miss—am 序列下与实际值相差 0.14,在 foreman 序列下与实际值相差 0.06,在 coastguard 序列下与实际值相差 0.33。

$PSNR_V/dB$  峰值信噪比:采用小波视频码率控制方法在 miss—am 序列下与实际值相差 5.48,在 foreman 序列下与实际值相差 4.2,在 coastguard 序列下与实际值相差 2;采用基于 CPLD 芯片控制方法在 miss—am 序列下与实际值相差 0.15,在 foreman 序列下与实际值相差 1.51,在 coastguard 序列下与实际值相差 0.27。

输出码率:采用小波视频码率控制方法在 miss—am 序列下与实际值相差 5.9,在 foreman 序列下与实际值相差 13.95,在 coastguard 序列下与实际值相差 8.84;采用基于CPLD芯片控制方法在 miss—am 序列下与实际值相差 0.09,在 foreman 序列下与实际值相差 0.11,在 coastguard 序列下与实际值相差 0.07。

综上所述:以 CPLD 芯片为基础的视频图像码率控制 策略最小控制误差为 0.07,由此也证实基于 CPLD 芯片的 视频图像码率控制方法的有效性。

(下转第94页)