Computer Measurement & Control

文章编号:1671-4598(2020)02-0140-04

DOI:10. 16526/j. cnki. 11-4762/tp. 2020. 02. 029

中图分类号: TP274.2

文献标识码:A

# 小型遥测数据采集存储装置设计

# 刘 倩,孝 雷,稆永志,孝芳培

(上海宇航系统工程研究所,上海 201109)

摘要:目前,运载火箭遥测系统多采用无线传输的方式,其信道具有一定带宽和容量限制;随着日渐增加的数据采集需求,原有遥测波道趋于饱和;为此,提出了一种小型遥测数据采集存储装置设计方案;该方案以FPGA作为核心控制模块,采用FLASH作为存储介质,可对待测信号进行采集、编帧以及存储;并采取了位置识别技术、分页存储技术、冗余设计等多种可靠性设计措施;该装置以低成本方式解决了现有遥测系统信道余量不足的问题,具有设计简便、可回收、体积小的特点,为后续运载火箭的设计改进提供了有效的数据支持,具备较高的通用性及可靠性。

关键词:数据采集;存储;FLASH

# Design of Small Telemetry Data Acquisition and Storage Device

Liu Qian, Li Lei, Zhang Yongjie, Li Fangpei

(Shanghai Institute of Aerospace System Engineering, Shanghai 201109, China)

Abstract: At present, the telemetry system of launch vehicle adopts radio transmission, and its channel has certain bandwidth and capacity limitation. With the increasing demand of data acquisition, the original telemetry channel tends to be saturated. A design scheme of small telemetry data acquisition and storage device is proposed. This device uses FPGA as the core control module and FLASH as the storage medium, and is used for signal acquired, framed and stored. Several reliability design measures such as location identification, paging storage and redundancy design are also adopted. The device solves the problem of insufficient residual amount of existing telemetry channel in a low—cost way. It has the characteristics of being easy—design, recyclable and small in volume, providing effective data support for the design and improvement of subsequent launch vehicles, and has high universality and reliability.

Keywords: data acquisition; storage; FLASH

# 0 引言

运载火箭飞行试验是运载火箭研制过程中的重要环节, 在飞行试验中,通过遥测系统采集记录火箭飞行试验中的 工作状态参数,进而评估火箭的各种技术指标。

随着航天技术的迅速发展,对运载火箭的运载能力提出了更高的要求。运载火箭外形尺寸和体积的增大,以及捆绑助推器等新状态,导致运载火箭遥测参数的数量和采样率都有了较大增长[1]。对于成熟型号运载火箭,为改进载荷能力,需要进行相关参数测量,从而为后续性能改进提供工程数据,这就需要对遥测数据波道进行调整。而现有测量波道已趋于饱和,如对已有数据采集设备进行更改会涉及到多个技术状态变化,不适用于高密度发射形势。对于新增测量需求,可将部分无实时性要求的测量参数通过存储器的形式事后获得,与无线传输方式相比,该种方式具有系统架构简单、获取数据可靠的优点,在飞行器飞行试验中具备广泛的应用[2]。

针对运载火箭不同技术状态下新增参数的测量需求,

收稿日期:2019-06-22; 修回日期:2019-07-31。

作者简介:刘 倩(1984-),女,河北沧州人,硕士,高级工程师,主要从事运载火箭电子设备设计方向的研究。

本文设计一种具备存储功能的小型数据采集装置。该装置 对运载火箭飞行过程中的多路参数进行采集并存储,待回 收后可通过专用测试设备对存储的数据进行读取并分析。 该种测试方法独立于现有遥测系统,不占用现有遥测系统 波道,并具有设计简便、可回收、体积小、可靠性高等特 点,可推广应用于多种型号运载火箭飞行试验过程中的参 数测量,为运载火箭设计改进提供技术基础。

# 1 系统设计

数据采集记录装置测量需求如下:

- 1) 测量路数: 16 路, 包含 4 路 2 kHz 的速变信号,以及频率不大于 15 Hz 的 12 路缓变信号;

- 2) 信号类型:幅值为0~5 V,采样精度为8位;

- 3) 测量时间: 不大于 200 s。

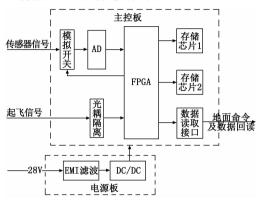

根据测量需求,设计原理如图 1 所示。数据采集记录装置由电源板和主控板组成。其中,28 V 电源由电池提供,电源板将 28 V 电源滤波后转换成主控板所需电压;主控板负责控制数据采集、编帧和存储任务。

主控板以 FPGA 为控制核心,控制模拟开关及 AD 转换器进行传感器信号的采集,并将采集到的数据存储至存储芯片中。为与系统时标进行统一,使用起飞信号作为数据采集存储动作的启动指令。为提高数据存储的可靠性,

在主控板上设置 2 块完全相同的存储芯片, 互为备份, 同时存储, 确保在回收时, 当其中一个出现故障, 另一个存储芯片能保证数据的完整回读。

数据采集记录装置与测试设备之间设置数据回读接口, 在数据回收时,接收测试设备命令,将测试数据通过数据 回读接口传输到测试设备进行分析。

图 1 数据采集记录装置原理框图

# 2 硬件设计

# 2.1 主控芯片选型

FPGA具有功能集成度高、逻辑资源丰富、可重复编程、速度快、效率高、设计灵活等优点,广泛应用于数字系统设计。本产品选用 Xilinx 公司生产的 XC3S500E 型芯片作为控制芯片来完成整机的功能和时序控制,该芯片具备丰富的逻辑资源,融合了 RAM 和用户 I/O,适用于大规模时序电路的开发和设计[3]。

上电初始化完成后,FPGA 周期性从其内部 RAM 中读 出帧格式信息。通过帧格式数据设置,可以更改不同信号 的采样频率,产生模拟开关以及 AD 控制信号,将采集到 的信号按帧格式编帧,存储至 FLASH 芯片,并提供芯片数 据的回收读数以及擦除功能。

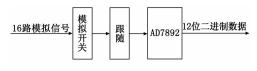

## 2.2 AD 及模拟开关选择

16 路传感器信号经模拟开关进行依次选通,接入到AD转换芯片进行转换,得到的二进制数据传输至FPGA进行存储和处理。模拟开关的切换由 FPGA 控制,在 FPGA内部设置帧格式,FPGA根据帧格式顺序依次打开模拟开关,对选通的相应路数的模拟信号进行 AD转换。通过改写帧格式数据,可对待测信号的采样频率以及采样顺序进行控制。

模拟开关选用 AD 公司的 ADG1206,该芯片由±15 V 供电,可对 16 路输入信号进行切换,典型切换时间为 80 ns,且封装小,有利于产品的小型化设计<sup>[4]</sup>。AD 转换芯片 选用 AD7892-1,该芯片具备 12 位分辨率,转换速率为 500 ksps,输入信号范围为-5~+5 V,自带参考电压模 块<sup>[5]</sup>。为保证采样精度,选用精度以及稳定度更高的外部 参考源 AD845 作为 AD7892 参考电压端的外部输入。为保 证阻抗匹配,模拟开关输出端通过电压跟随器 LM110 连接到 AD 芯片输入端。

图 2 AD转换原理框图

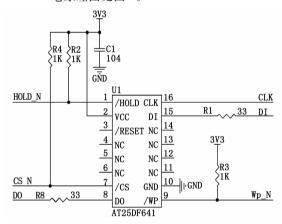

#### 2.3 存储芯片选择

常用的非易失性存储芯片有 E²PROM、NorFlash、NandFlash等,其中 E²PROM 的写入速度较慢,NandFlash需要特殊的控制接口和软件算法,均不适合本数据采集记录装置的应用。设计中选用 Atmel 公司的 AT25DF641,该芯片为 SPI 型 FLASH,具有引线少、接口简单、使用方便的优点。芯片存储容量为 64 Mbit(8MByte),单字节典型编程时间为 7 μs,单页(256Bytes)最大编程时间为 3 ms。芯片在使用前需执行擦除操作,擦除操作可按扇区、块或整片执行,芯片的擦除寿命为 10 万次<sup>[6]</sup>。由于擦除操作耗时较长,设计时在写入操作前先进行整片 FLASH 的擦除。AT25DF641 电原理图见图 3。

图 3 存储芯片电原理图

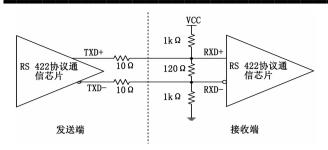

## 2.4 数据回读接口设计

数据回读接口用于在回收时读取 FLASH 中的数据,并可以在数据采集时对 FLASH 状态进行监控,以及通过测试设备对数据采集记录装置发出指令进行控制。硬件接口采用 RS422 模式,接口原理图见图 4。电路设计中,对于输入信号,采用  $120~\Omega$  终端匹配电阻来进行阻抗匹配,并添加 1 K $\Omega$  的上下拉电阻,当输入信号处于未连接或意外断开的状态时,接收端有固定的差分输入电压。对于输出信号,为避免输出端意外短路,串接  $10~\Omega$  的保护电阻。RS422 电路具备较强的抗共模干扰能力,信号容差性好,且接口协议可自定义,在多种数据通信场合得到广泛应用[7]。

### 2.5 电源模块设计

电源板为整机供电,28 V 一次电源经电磁滤波器 EMI 滤波后,输入至  $16\sim40$  V 宽输入开关电源 DC/DC 模块,产生控制板所需的二次电源±15 V 及+5 V。

图 4 RS422 接口原理图

EMI 滤波器用在电源模块的输入端,其主要作用是抑制 DC/DC 的开关噪声对电源母线产生干扰,同时抑制 DC/DC 端的共模和差模干扰,以及对内部 DC/DC 进行防过压和防过流保护。DC/DC 模块为换流模块的核心电路,主要功能是将一次电源 28 V 电压,隔离后转换成测量系统所需要的±15 V 以及+5 V 电压,同时功率与电压输出品质满足系统负载使用要求。根据负载评估结果及电源品质输出要求,同时选择成熟可靠厂家产品,采用 Interpoint 公司的DC/DC 芯片。该公司 DC/DC 芯片同时具备短路保护、输入输出电气隔离、以及耐 50 V 瞬时冲击的特性,成熟度较高,经过国内外多发飞行试验的考核。

# 3 软件设计

数据采集记录装置的软件功能主要包括:根据起飞信号到来时间,以及帧格式要求,控制模拟开关及 A/D 转换,进行模拟信号采集,将采集到的数据存储至 FLASH中;通过 RS422 接口接收测试设备命令,在回收后,读取 FLASH 中存储的数据。软件功能框图见图 5。

图 5 软件功能框图

#### 3.1 帧格式设计

根据对测量需求的分析,需采集的信号包括 4 路 2 kHz 的速变信号,以及 12 路缓变信号。根据采样定理,为保证采样质量,采样频率至少为信号频率的 2 倍,同时考虑到FLASH 芯片 AD25DF641 的页编程字节数为 256,为此设计如下帧格式:

- 1) 副帧长度: 50; 子帧长度: 10; 全帧字数: 500;

- 2) 字长: 8 bits, 码速率: 200000 bps (25 K Byte/s);

- 3) 副帧采样率: 50 Hz; 子帧采样率: 2.5 kHz;

- 4) 测量时间: 200 s, 总数据量: 5 M Bytes。

其中,每路速变信号占2个子帧,采样率为5 kHz。缓变信号在每个副帧中采样一次,采样率为50 Hz。同时,在帧格式中添加帧同步标识以及帧计数,防止丢帧以及误帧情况。

为节省硬件空间,帧格式数据放置于 FPGA 内部。FP-GA 在进入采集模式后,周期性地从帧格式存储空间读取通道号和通道类型,根据类型产生不同的时序。通道类型包括待采信号、帧同步、帧计数以及空波道等。当信号采集需求发生变化时,通过更改帧格式数据文件即可实现不同采样率的控制。

#### 3.2 模拟开关及 A/D 转换控制

由于模拟开关的切换需要一定的稳定时间,软件设计时预留足够的时间,保证模拟开关稳定以后,再进行 A/D 转换。

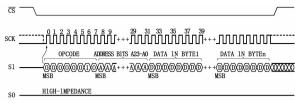

A/D芯片 AD7892 转换时序见图 6,在 CONVST 信号的上升沿,采样保持器进入保持状态,并开始 A/D 转换。经过一定的转换时间  $t_{CONV}$ 后,EOC 信号输出负脉冲表明转换结束。当 CS、RD 信号有效,经过  $t_6$  时间后,即可在数据总线上获得 12 位数据。12 位数据全部送入 FPGA,可根据采样精度需求,选取相应位数进行编帧。本设计为 8 位字长,且由于输入的模拟信号为  $0\sim5$  V,故选取第 11 至第 4 位进行存储。

图 6 A/D转换软件时序图

#### 3.3 FIFO 选择

根据对帧格式的分析,每帧数据大小为500字节,时长为20ms。对FLASH存储芯片AT25DF641进行写操作时,需要写控制字、写数据和编程,这些都需占据一定时间。在此期间采集的数据是连续不断送来的,需要使用FIFO进行缓存,否则会丢失该时间段内的参数。为得到最快的写FLASH速率,选用页编程模式,每次可对256Bytes的数据进行编程,最大页编程时间为3ms,设计时选用512Bytes的FIFO进行数据的缓存。基于系统集成化的考虑,选用FPGA内部FIFO,充分利用了FPGA强大的资源,减小了系统体积,同时节省硬件成本[8]。

#### 3.4 FLASH 控制

对 FLASH 芯片 AT25DF641 的操作包括擦除、写操作 以及读操作。对于写操作来说,在每次编程前要先进行写 使能,允许对芯片进行编程操作,然后发送页编程命令、地址以及需要写到 FLASH 中的数据。页编程命令时序图见图 7。AD25DF641 可自动检测、报告编程或擦除失败,在编程结束时可通过读相关寄存器来查询编程是否成功,如 没有编程成功,则将该页地址写入 FLASH 特定地址,供回 收数据时参考。

# 4 可靠性及关键技术

#### 4.1 结构可靠性设计

数据采集记录装置需要经过硬回收,工作环境恶劣,

图 7 FLASH 页编程时序图

如高冲击过载、高温、高压等,易对内部电子器件造成损害<sup>[5]</sup>。数据采集记录装置在落地硬回收的过程中,一方面因与地面撞击,会产生巨大的撞击力,需要对壳体进行抗高过载防护设计;另一方面,因数据采集记录装置在随舱段飞行过程中,具有较高的动态性能,对其内部电路产生较大的惯性作用力,因此需要在壳体内部设置多层缓冲材料,并对印制板进行灌胶处理。

通过特殊的结构设计和电装工艺,确保产品可耐受大剂量冲击应力,确保随火箭箭体坠落至地面时产品不损坏,从而可靠回收数据。

#### 4.2 软件可靠性设计

数据在回收后需要进行分析,对飞行过程中的重要参数进行还原。所以应保证数据采集记录装置工作的稳定、可靠[10]。设计时采用以下技术:

- 1) 位置标识技术:每帧数据为 500 Bytes,FLASH 芯片 AT25DF641 每页包含 256 Bytes,因此在存储时把每帧数据均分为 2 块,在每一块数据的末尾加上 6 个字节的位置信息,记录本块数据的具体位置,在数据回收时可方便的进行参数的恢复,避免由于外界干扰导致的数据丢失。

- 2) FLASH 分页存储技术:每帧数据占据的存储空间为2页,软件在进行到写数据模式时,先顺序检测每页是否有数据,如有则跳至下一页地址,直至跳转至空白页进行数据写入。这样一方面保证不会覆盖已写入的数据,另一方面避免频繁的对 FLASH 芯片初始地址的页面进行操作,造成芯片损坏。

- 3) 冗余设计:为提高数据存储的可靠性,在主控板上设置 2 块完全相同的存储芯片,互为备份,同时存储,确保在回收时,其一出现故障,另一个存储芯片保证数据的完整回读。

#### 5 试验结果与分析

数据采集记录装置以"起飞"信号为起点开始记录数据,与系统时标起点统一。当数据采集试验结束后,从数据采集记录装置中回收数据,以起飞信号作为起点,结合帧格式来绘制波形,可以得到16路传感器信号在200s内的变化趋势。

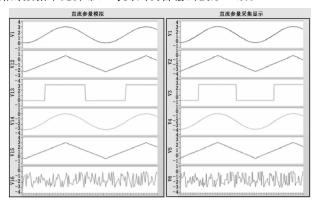

为验证测试数据采集记录装置的功能性能,设计生产了原理样机,使用测试设备模拟传感器信号,包括正弦波、方波、三角波等。数据采集记录装置对上述波形进行采集,结束后进行数据回收,并用上位机软件对数据进行波形绘

制,输入及输出波形见图 8。可见,数据采集记录装置中存储的数据未见异常,与测试设备输出波形一致。

图 8 测试波形图

#### 6 结论

本文介绍了一种具备存储功能的遥测数据采集装置的设计方法及其可靠性设计。该装置可对多路信号进行采集、编帧及存储,并在数据存储时采用了位置标识、分区存储、冗余设计等技术,能够可靠地进行数据存储及回收分析,为后续运载火箭的设计改进提供了有效数据支持。该装置设计灵活,节省了无线信道带宽,提高了运载火箭数据获取的准确性与可靠性,以低成本、低风险的方式解决了现有遥测波道余量不足的问题,具有一定的推广价值。

#### 参考文献:

- [1] 张晨光, 吕 明, 王 刚. 运载火箭遥测数据处理研究 [J]. 导弹与航天运载技术, 2005 (2): 9-11, 48.

- [2] 王小东, 郝志航. 大容量固态存储技术 [J]. 光学精密工程, 2001, 9 (4): 396-400.

- [3] 刘 洋,姜秀杰. 基于 FPGA 的空间电场信号采集系统设计 [J]. 现代电子技术,2012,35 (19):56-58.

- [4] ADG1206. Low Capacitance, 16—and 8—Channel ±15V/+12 V iCMOS™ Multiplexers [Z]. Analog Devices, 2006.

- [5] 程耀瑜,胡 鷗,高速 12 位模数转换器 AD7892 及其在图像采集中的应用[J]. 国外电子元器件,2000(9):22-24.

- [6] 张燚翾,殷希梅,程洪涛.基于 AT25DF641 的弹载数据记录器的设计 [J]. 弹箭与制导学报,2010,30 (5):209-210,214.

- [7] 王俊超,王恒亮.基于 FPGA 的参数可调 RS422 接口电路设计 实现 [J], 电子科技,2015,28 (2):134-138.

- [8] 陈 靓, 孙运强. 基于 FPGA 的多路数据采集系统设计 [J]. 装备制造技术, 2009 (12): 59-61.

- [9] 李寿安,李曙林,何卫锋.某型飞行数据记录器防护壳体优化设计[J].沈阳航空工业学院学报,2002,19(2):8-9.

- [10] 史玉健,任勇峰,李辉景,等. 基于 FLASH 的高速数据记录器的研究与设计 [J]. 计算机测量与控制,2011,19 (12):3158-3160.