文章编号:1671-4598(2017)08-0304-05

DOI:10. 16526/j. cnki. 11-4762/tp. 2017. 08. 078

中图分类号:TN911

文献标识码:A

# 基于国产 FPGA 及 DAC 的任意波形 发生器的设计

高野军<sup>1</sup>、武福存<sup>2</sup>

(1. 北京航天长征飞行器研究所,北京 100076; 2. 北京航天测控技术有限公司,北京 100041)

摘要:任意波形发生器作为测试测量设备的一种重要仪器,在航空航天的测量与控制技术领域中得到了广泛应用;当前市场成熟任意波形发生器产品多为国外产品或者国内厂商基于国外 FPGA 和 DAC 研制的产品;为了打破技术垄断,提高国产任意波形发生器的自主技术保障能力,研制基于国产芯片的任意波形发生器愈发重要;随着国产芯片设计技术提升,国产 FPGA 和 DAC 的性能显著提高,并得到了广泛应用;PXI 总线作为当前仪器领域的主要总线类型之一,可以满足大部分测试仪器的通讯要求;基于国产 FPGA 和 DAC 器件,从硬件设计和软件设计两个方面出发,成功研制了一款采样率为 100 MSa/s 的 PXI 总线任意波形发生器模块,实现了 43 MHz 信号输出,通过实验测试了模块的功能和性能,完全满足模块指标要求,充分证明了国产芯片在工程设计中的性能特性。

关键词:任意波形发生器;国产 FPGA; PXI 总线;国产高速数模转换器

# Design of the Arbitrary Waveform Generator Based on Domestic FPGA and DAC

Gao Yejun<sup>1</sup>, Wu Fucun<sup>2</sup>

(1. Beijing Institute of Space Long March Vehicle, Beijing 100076, China;

2. Beijing Aerospace Measurement & Control Technology Co. , Ltd. , Beijing 100041 , China)

Abstract: Arbitrary waveform generators are important instruments for testing and measuring equipment, and they are widely used in the field of current measurement and control technology of the aerospace. The current market mature arbitrary waveform generators are foreign products or domestic manufacturers based on foreign FPGA and DAC developed products. In order to break the monopoly of technology, and improve the domestic arbitrary waveform generator of independent technical support capabilities, it is more important to develop arbitrary waveform generators based on domestic chips. With the improvement of domestic chip design technology, the performance of domestic FPGA and DAC has been improved, and has been widely used. The PXI bus, as one of the main bus types in the current instrument area, meets the communication requirements of most test instruments. Based on domestic FPGA and DAC, from the hardware design and software design two aspects, successfully developed a PXI bus arbitrary waveform generator module with sample rate up to 100MSa/s, and output a 43MHz signal. Through the test of the function and performance of the module, fully meet the requirements of the module indicators, fully proved that the domestic chip in the engineering design of the performance characteristics.

Keywords; arbitrary waveform generator (AWG); domestic FPGA; PXI Bus; domestic DAC

# 0 引言

任意波形发生器是一种特殊的信号源,任意波形发生器通过读取查找表的数据样本点,来创建函数波形和任意波形。大多数现代任意波形发生器 采用直接信号合成 (DDS) 技术,在广泛的频率范围上提供信号。

测控总线是指以组成测量和控制系统为主要目标而开发的总线。自数字计算机问世以来,各种总线标准不断推出,如PC、ISA、PCI总线。PCI总线支持64位和32位数据总线,其64位数据地址复用总线能使系统的带宽达到264 MB/s。CPCI总线是PCI总线在工控领域的扩展,PXI总线是CPCI在仪器领域的扩展,它不仅保留了PCI总线较高的数据吞吐

收稿日期:2017-04-25; 修回日期:2017-05-11。

作者简介:高野军(1968-),男,辽宁人,高工,主要从事无线电测试与控制方向的研究。

能力,而且采用了坚固的欧洲插卡组装技术。

目前国内外厂商已经研制了很多基于 PXI 总线的任意波发生器模块[1-4]。测试对象的性能提升及恶劣的测试环境对任意波形发生器的技术要求越来越高,现有的 PXI 总线任意波发生器大都基于 FPGA 及 DAC 进行开发设计。而 FPGA 产品主要厂商为 ALTERA 和 XILINX,DAC 产品的主要厂商为美国的 ADI 和 TI 公司,所以目前国产的任意波发生器模块关键芯片严重依赖进口。因此基于国产 FPGA 和国产 DAC 芯片开发高性价比任意波发生器模块具有重要意义。

#### 1 任意波形发生器总体设计方案

本论文的主要任务是基于国产 FPGA 和国产 DAC 研制采样率为 100 MSa/s 的单通道任意波形发生器模块。因为基于 PXI 总线模块化仪器具有严格的电气特性和机械结构特性,本论文主要从以下两个方面进行设计:首先是在硬件结构设计方面,对于尺寸为 3U的 PXI 模块设计,应该要充分考虑它的仪

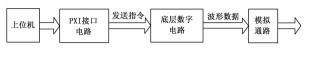

器小型化设计,其次是在软件功能方面,上位机将数据信息和控制命令通过 PXI 总线传送到下位机进行输出波形,要考虑下位机数字电路部分配合作用<sup>[5-8]</sup>。任意波形发生器整体结构如图 1 所示。

图 1 任意波形发生器整体结构

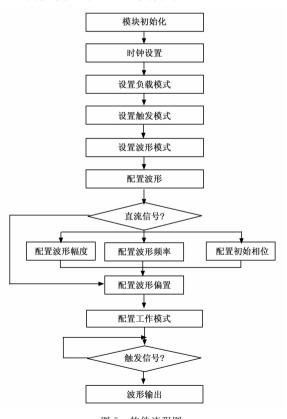

#### 1.1 任意波形发生器工作流程

任意波形发生器的主要工作流程:用户通过上位机软件控制 PXI 模块进行波形、频率、幅值等参数的选择,经由 FPGA 芯片实现的 PXI 接口和逻辑控制单元将波形数据信息写到板上大容量数据存储器上,存储器的存储空间应与 PXI 总线通道采样点的数字量应该保持一致。上位机软件设置启动完成后,底层控制逻辑以 DDS 方式对存储器进行访问,并将存储区的波形数剧读出至高速 DAC,以实现数字量向模拟量的转换,转换后的模拟信号通过模拟通路的调理到达输出端,最终实现波形的输出。

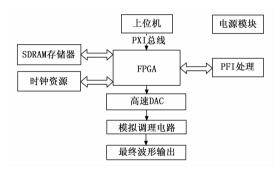

主要工作流程如图 2 所示。

图 2 硬件由路工作流程框图

#### 1.2 任意波形发生器硬件总体设计方案

任意波形发生器硬件电路主要由 PXI 接口电路、FPGA 主控电路、高速存储电路、高速 DAC 电路、模拟调理电路、时钟电路等多部分组成。FPGA 主控电路是电路的核心部分,它完成了 FPGA 外围电路配置,通过 PXI 总线与上位机进行通信,使 FPGA 能够执行上位机发送的数据指令;作为控制器,实现对存储电路的读写操作,完成高速 DAC 电路的初始化,并且输出数字波形给 DAC,其内完成了下位机几乎所有的逻辑控制。高速存储电路作用存储上位机发送过来的数据以及读出 SDRAM 数据到 FPGA 中去。高速 DAC 电路作用是将 FPGA 传输出来的数字波形转换成模拟波形。模拟调理电路完成的功能是对 DAC 输出的模拟波形进行滤波、放大等调理,使最终的输出波形能够满足设计的预期指标。硬件总体组成如图 3 所示。

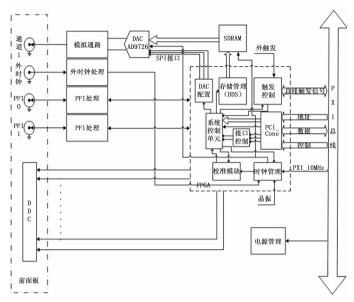

FPGA 控制逻辑组成分为 PCI\_CORE、接口控制、系统控制单元、存储管理、触发控制、时钟控制、DAC 配置及校准等 IP 模块。

1) PCI\_CORE: 采用标准的 PCI 总线 IP 核,实现 33 MHz, 32bit 的总线通讯控制,实现上位机对下位机的命令

图 3 硬件总体组成

控制。

- 2) 系统控制单元:完成本地总线命令译码,实现 FPGA内部逻辑的读写控制及状态监测。

- 3)存储管理:本次模块要求实现 64 MSa 点、100 MSa/s 采样率,而当前国产 FPGA 仅支持 SDRAM 大容量存储器, 为实现存储指标要求,模块设计中采用两片 SDRAM 位扩展模 式,即两片 SDRAM 共享控制总线和地址总线,数据总线独 立,从而降低了 SDRAM 的工作速率,降低了逻辑设计难度。

- 4) 触发控制:模块具有丰富的触发源和触发模式。触发源支持软件触发、外触发及背板触发等,触发模式支持单次触发、连续触发及突发触发等,为了实现上述功能,开发设计触发控制 IP。

- 5) 时钟控制:模块支持内时钟、外时钟及背板时钟等多种采样时钟源和多种参考时钟源选择,开发设计的时钟控制IP圆满解决了时钟功能要求。

- 6) DAC 配置: DAC 芯片的功能配置支持 SPI 配置模式,通过 DAC 配置 IP 实现 DAC 内部寄存器的命令控制及状态读写。

#### 1.3 任意波形发生器软件总体设计方案

任意波形发生器软件总体设计方案主要是底层数字电路部分 FPGA 内部逻辑编程,其是对上位机通过 PXI 总线发送到下位机的数据信息进行设计编程。

IVI 规范是 PXI 总线模块化仪器软件开发的基本标准,为了更好的兼容国外产品,任意波形发生器模块驱动软件开发时,其函数命名及参数定义,严格按照 IVI-Fgen 规范要求,便于直接替换现有系统的国外产品。

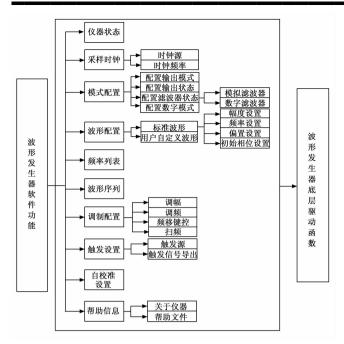

上位机的软件体系架构如图 4 所示,主要描述了上位机与板卡间的通信实现。

软面板主界面主要显示波形参数选项、输出参数配置、触 发配置及调制功能选项;系统菜单中主要包含了PFI设置、采 用时钟设置、自校准功能及退出功能,帮助菜单提供仪器的基

图 4 软件体系结构

#### 本信息及帮助文件。

图 5 为任意波形发生器的软件流程图。

图 5 软件流程图

#### 1.4 PXI 总线接口设计方案

PXI 总线接口的作用是在 PXI 模块中完成 PXI 底板总线 与功能电路之间的通信传递(逻辑时序的转换),是 PXI 总线 与功能电路之间的桥梁。通常情况下 PXI 总线接口设计的方 案主要有两种:一种方案是采用业界已经成熟的专用 PXI 接 口芯片进行设计;另一种方案则是利用 FPGA/CPLD 等可编 程逻辑器件进行编程实现与电路设计。本文采用第二种方案。 FPGA 设计 PXI 接口方案最主要的优势就是使用灵活,用户可 以根据自身的需求进行自由设计,在可编程逻辑器件中完成自 行配置,节省 PCB 空间。

#### 2 任意波形发生器硬件设计

####

本次设计中选用的北京微电子技术研究所的国产 FPGA 芯片, 型号为 BQ2V3000-4bg728i, 其与 XILINX 公司 Virtex - II 的 xc2v3000 兼容。该芯片内核电压为 1.5 V, 共有 3145728 个系统门,可编程 IO 管脚 516 个,内部存储单元为 1769472 bits, 具有 300 MHz 的内部时钟速度。这款芯片配置 高达有 12 个 DCM 模块。使用 XILINX 公司的 ISE10.1 作为 FPGA 的开发工具,它支持 VHDL、Verilog 和原理图的输入。 在本次设计中, FPGA 芯片主要实现 PXI 接口通信和模块功能 逻辑电路的时序控制。

# 2.2 高速 DAC

高速 DAC 电路的作用是完成数字信号到模拟信号转换。 本次设计采用的是北京微电子研究所(772 所)研制的高性 能 16 位数模转换器 (DAC) 芯片 B9726, 其性能和封装完全 兼容 AD 公司的 AD9726, 且器件设计时采用了特有的辐射加 固技术, 抗总剂量的能力不小于 1000 Gy (Si), 单粒子锁定 (SEL) LET 阈值大于 75 MeV·cm2/mg。B9726 是一款,转 换速率可以达到 400 MSPS, 具有良好的噪声和杂散抑制性 能。数模转换器的16位数据端使用的是低电压差分信号 (LVDS) 输入,并且包含 100 Ω的内部端接电阻。LVDS的 时钟输出采用在双通道数据速率(DDR)模式下驱动外部 数据。

B9726 外围电路有 80 个引脚, 其中有 32 个引脚是数据输 入引脚, 时钟引脚有 6 个, 有 4 个 SPI 通信引脚, 有 2 个引脚 是输出电流引脚,还有1个复位引脚。在本次设计中,使用到 的引脚就只有上面那些引脚, 而其他的引脚或是接地或是接电 源信号。32个数据引脚被用作16位数据输入,输入方式是采 用LVDS低压差分方式传输,每位数据用两根信号线的差分 信号传输。

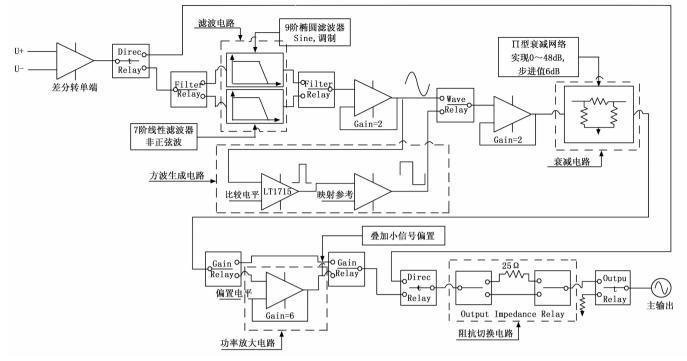

## 2.3 模拟调理电路设计

模拟调理电路实现了输出信号的各种调理功能,对输出信 号的幅频特性起到决定性作用,是满足系统预期指标的重要电 路组成部分。模拟调理电路主要由滤波电路、方波生成电路、 衰减电路、功率放大电路、阻抗切换电路及其他辅助电路组 成,模拟通路如图6所示。

模拟通路调理流程: DAC 转换后的波形信号输入运放电 路,将差分输入转换为单端输出。运放输出信号输入至滤波电 路,滤波电路分为两种滤波器:椭圆滤波器及线性相位滤 波器。

若主输出信号包含 Sine 类波形时选择椭圆滤波器滤波, 若主输出信号包含脉冲类信号或任意波时选择线性相位滤波器

图 6 模拟调理电路

滤波。滤波后的主信号输入初级放大,使主信号幅度放大至 2 Vpp。此时主信号分为两个支路: 1) Sine & Arb 输入后级调理; 2) Sine & Arb 输入比较器 (Sync 和方波频率控制) 产生方波频率控制信号。Square \_ Freq 通过电子驱动器 Edg211 映射后,形成方波信号 Square。

Sine & Arb 或 Square 经继电器选择后,输入至后级运算放大器,经调节后主信号输入衰减电路 (0~48 dB 衰减,步进 6 dB),若输出主信号为小信号时则直接输出至输出使能继电器,若输出主信号为大信号时则输入至 6 倍增益功率放大电路放大后再至输出继电器,最后通过控制输出使能继电器控制信号输出。

DC 信号或 AC 信号偏置通过 6 倍增益放大器实现,避免了偏置信号随 AC 信号幅度变小而变小的限制;方波信号采用映射方式实现,避免出现方波脉宽不稳定;为满足用户视频信号传输特性要求,输出增加  $75~\Omega$  输出阻抗方式。

#### 2.4 时钟处理

外时钟输入端口主要为仪器提供外部采样时钟及 PLL 参考时钟。设计时输入阻抗设定为  $50~\Omega$ , AC 耦合方式,为了尽可能减少输入信号的类型限制,采用高速比较器对输入信号过零比较产生同频时钟。

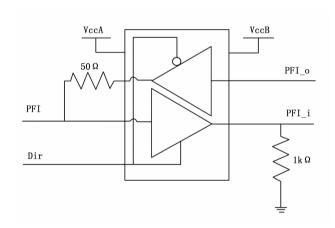

#### 2.5 PFI 处理电路

PFI0 及 PFI1 均为双向端口,作为输入时,接受外部触发信号,输入阻抗设定为  $1 k\Omega$ ;作为输出时,输出标识信号、触发启动信号、PLL 参考时钟导出信号及采样时钟导出信号,输出阻抗设定为  $50 \Omega$ 。

设计中采用双向缓冲器进行处理,其原理如图 7 所示。

#### 2.6 电源管理

电源是仪器正常工作的基础, 良好性能的电源电路设计能

图 7 PFI 处理原理框图

为仪器性能提高基本保障。仪器中使用到了+3.3 V、+1.2 V、+0.9 V、+1.8 V、+5 V、-5 V、+15 V、-15 V,PXI 背板可提供 $\pm12$  V、+5 V、+3.3 V,其余电源使用开关电源及 LDO 转换生成。

±15 V 电源用于功率放大电路, 仪器工作时对电流要求较高, 考虑 PXI 背板的供电情况,设计中采用升压一降压方式实现+5 V 转换出±15 V 电源。

#### 3 任意波形发生器软件部分设计

#### 3.1 FPGA 开发环境概述

本次设计中,使用的 FPGA 芯片是国产 FPGA 并且兼容 XILINX 公司的 Virtex\_ II 架构, 所以本次设计选用的开发环境是 10.1 版本的 ISE 软件。

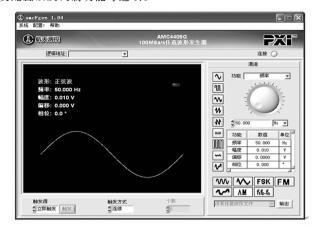

#### 3.2 上位机控制面板设计

上位机的设计采用 LabWindows/CVI 软件,系统界面如

图 8。面板主界面主要显示波形参数选项、输出参数选项、触发配置以及调制功能等选项。

图 8 系统面板界面

# 4 结果测试与分析

系统测试主要是针对任意波信号发生系统要求的指标进行 测试,以及测试系统的稳定性等。

#### 4.1 波形种类测试

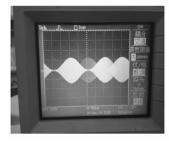

系统模块可以实现多种标准波形、任意波、调幅、调频等 波形,具体波形如图,如图 9~12。

图 9 正弦波

图 10 任意波

图 11 调幅

图 12 调频

#### 4.2 波形频率测试

以正弦波为例对其波形频率测试,在全频率范围内选择典型频率值进行测试,对应测试结果见表 1。

从表 1 中可以看出,正弦波的波形频率输出范围在 10~40 MHz 之间,频率准确度在 5 ppm 之内。

表 1 正弦波频率测试结果

| 理论值   | 实测值           | 准确度    |

|-------|---------------|--------|

| 1Hz   | 0.9999975Hz   | 2.5ppm |

| 1KHz  | 999. 9969Hz   | 3.1ppm |

| 1MHz  | 999996.6Hz    | 3.4ppm |

| 40MHz | 39. 999861MHz | 3.5ppm |

# 4.3 波形幅度测试

以正弦波为例对其波形幅度测试,在全幅度范围内选择典型幅度值进行测试,对应测试结果见表 2。

从表 2 中可以看出,正弦波的波形幅度输出范围在 10~mV  $\sim 10~\text{V}$  之间,在误差允许范围之内,输出波形满足指标要求。

表 2 正弦波幅度测试结果

| 理论值              | 实测值    | 误差   |

|------------------|--------|------|

| $10 \mathrm{mV}$ | 10.1mV | 1%   |

| 1 V              | 1.01V  | 1%   |

| 10 V             | 10.16V | 1.6% |

# 5 结论

根据模块测试结果可知:国产 FPGA 及国产 DAC 完全满足本次任务开发需求。设计中单片 FPGA 控制两片 SDRAM, FPGA 内部的 DDS 采用 48 位累加器工作模式,共使用了 4 个DCM 模块,此时 DDS 运行时钟仍然可以达到 125 MHz,而DAC 芯片 B9726 在其他项目中应用时可以稳定实现 400 MSPS 采样率,且测试结果可媲美国外同类产品。

本模块的研制在保证基本性能的前提下, 充分使用并验证 了国产器件的性能, 为其他国产化需求产品的研制提供了前瞻 性意义。本文研制的任意波形发生器已在多个项目中得到了广 泛应用。

#### 参考文献:

- [1] 柳肖杰. PXI200MSPS 任意波形发生器数字电路设计 [D]. 成都:电子科技大学,2012.

- [2] 邱大强. 基于 PCI 总线的任意波形发生器 [D]. 成都: 西华大学, 2008.

- [3] 铁 奎,黄 武. 任意波形发生器的研究与设计 [J]. 国外电子 测量技术, 2012, 31 (6): 80-83.

- [4] 付 洁. 基于 FPGA 的 PXI 接口的 DDS 信号发生器的设计 [D]. 西安: 西安电子科技大学, 2014.

- [5] 朱松涛, 张 怡. 基于 FPGA 的 PCI 总线接口设计 [J]. 计算机工程与应用, 2006, 24 (09): 14-39.

- [6] 周俊峰,陈 涛. 基于 FPGA 的直接数字合成技术器的设计与实现[J]. 电子技术应用, 2002, 28 (12): 74-75.

- [7] 陈立克. 基于 Xilinx FPGA 设计技术的应用研究 [D]. 兰州: 兰州大学, 2011.

- [8] 刘东华. Xilinx 系列 FPGA 芯片 IP 核详解 [J]. 北京: 电子工业 出版社, 2013.